You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4355

[filter] => raw

[cat_ID] => 157

[category_count] => 4355

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

In the rapidly evolving semiconductor industry, Design Rule Checking (DRC) remains a critical bottleneck in chip design workflows. Siemens EDA’s presentation at the 2025 TSMC Open Innovation Platform Forum, titled “AI-Driven DRC Productivity Optimization,” showcases how artificial intelligence … Read More

As AI and HPC systems scale to thousands of CPUs, GPUs, and accelerators, interconnect performance increasingly determines end-to-end efficiency. Training and inference pipelines rely on low-latency coordination, high-bandwidth memory transfers, and rapid communication across heterogeneous devices. With model sizes… Read More

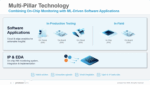

I’ve blogged about Methodics before they were acquired by Perforce back in 2020, so I wanted to get an update on Perforce IPLM (Integrated Product Lifecycle Management) by attending their recent webinar. Hassan Ali Shah, Senior Product Manager and Rien Gahlsdor, Perforce IPLM Product Owner were the two webinar presenters. Their… Read More

At advanced nodes, the clock is no longer just another signal. It is the most critical and sensitive electrical network on the chip, and the difference between meeting performance targets and missing the tape-out often comes down to a few picoseconds, buried deep inside the clock distribution network. Yet many design teams still… Read More

Modern chip design has reached unprecedented levels of complexity. Today’s System-on-Chip (SoC) designs integrate multiple processors, complex memory hierarchies, sophisticated interconnects, and much more. All requiring orchestration using complex EDA tool flows. Months are routinely lost to configuration… Read More

At times it has seemed like any development in EDA had to build a GenAI app that would catch the attention of Wall Street. Now I see more attention to GenAI being used for less glamorous but eminently more practical advances. This recent white paper from Siemens on how to help verification engineers get up to speed faster with PSS is … Read More

For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes… Read More

The natural language understanding now possible in LLMs has raised interest in using specs as a direct reference for test generation, to eliminate need for intermediate and fallible human translation. Sadly, specs today are not an infallible source of truth for multiple reasons. I am grateful to Shelly Henry (CEO of MooresLab)… Read More

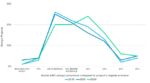

In the competitive vertical of mobile System-on-Chip development, SRAM plays a pivotal role, occupying nearly 40% of chip area and directly impacting yield and performance. The presentation “Accelerating SRAM Design Cycles With Additive AI Technology,” co-delivered by Mohamed Atoua of Siemens EDA and Deepesh… Read More

SoC projects are running behind schedule as design and verification complexity has increased dramatically, so just adding more engineers, more tests and more compute aren’t the answer. The time is ripe to consider smarter ways to improve verification efficiency. The added complexity of multiple embedded processors, multiple… Read More

The Quantum Threat: Why Industrial Control Systems Must Be Ready and How PQShield Is Leading the Defense