This is it! This is the single page of code that Ákos Hadnagy wrote this summer to formally verify WARP-V, an open-source RISC-V CPU core.… Read More

Electronic Design Automation

Design Compiler – Next Generation

Back in 1986, Synopsys started out with a synthesis product by name of SOCRATES, which stands for Synthesis andOptimization ofCombinatorial logic usingRule-basedAndTechnology independentExpertSystem. It is fair to say that not many designers know that was the birth name of what eventually turns out to be a very successful… Read More

Webinar: Tanner and ClioSoft Integration

A fusion of digital and analog IC circuits, mixed signal ICs are key components to many applications including IoTs, automotive, communications and consumer electronics –acting as enabler to bidirectional conversion of signals between analog domain derived from various audio, temperature and visual sensors to digital… Read More

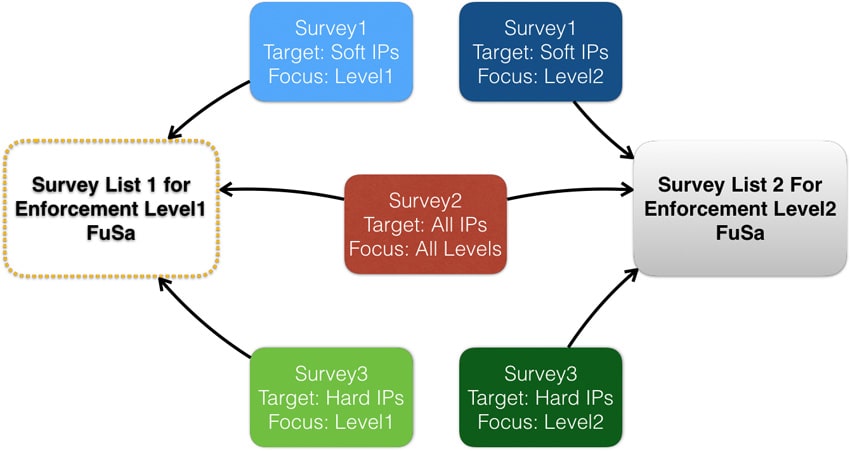

Using IP in a SoC Compliant with ISO 26262

The automotive segment is being well served by semiconductor suppliers of all sizes because of the unit volumes, and the constant push to automate more of the driving decisions to silicon and software can raise lots of questions about safety, reliability and trust. Fortunately the ISO standards body has already put in place a functional… Read More

I Thought that Lint Was a Solved Problem

A few months back, we interviewed Cristian Amitroaie, the CEO of AMIQ EDA. We talked mostly about their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and how it helps design and verification engineers develop code in SystemVerilog and several other languages. Cristian also mentioned… Read More

Eliminate PCB Re Spins using an Integrated Multi Dimensional Verification Platform

The rapidly increasing complexity of today’s designs, combined with schedule pressure to deliver innovative products to market as quickly as possible, strains engineering resources to the limit, often to the point of breaking. As a result, 17% of all projects get canceled, and another 28% miss their target release date (Source:… Read More

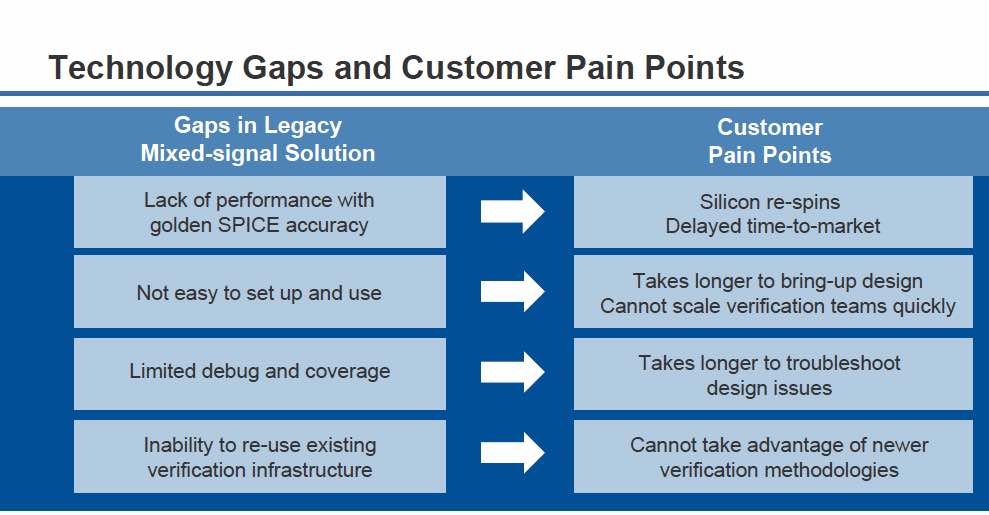

Mentor’s Symphony in Tune with AMS Designer Needs

Mixed signal simulation is a very hot topic these days. In modern designs, it is harder to draw a line between the analog and digital and work with them independently. Analog blocks are showing up everywhere. Even in what would have qualified as a digital design a few years ago, now designers need to look at things like PLLs, IOs and … Read More

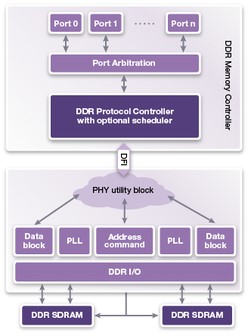

Synopsys DDR5 LPDDR5 Memory Interface IP Targets AI, Automotive, and Mobile SoCs

Synopsys announced on October 24 new DesignWare[SUP]®[/SUP] Memory Interface IP solutions supporting the next-generation DDR5 and LPDDR5 SDRAMs. The DDR5 and LPDDR5 IP significantly increase memory interface bandwidth compared to DDR4 and LPDDR4/4X SDRAM interfaces, while reducing area and improving power efficiency.… Read More

Fusion Synthesis for Advanced Process Nodes

Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited… Read More

DAC 2019 to Host the Second System Design Contest!

Interested in showing off your talent in developing deep learning algorithms on embedded hardware platforms for solving real-world problems? Join the second System Design Contest (SDC) at the 56[SUP]th[/SUP] Design Automation Conference in 2019!… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center