You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 157

[name] => EDA

[slug] => eda

[term_group] => 0

[term_taxonomy_id] => 157

[taxonomy] => category

[description] => Electronic Design Automation

[parent] => 0

[count] => 4440

[filter] => raw

[cat_ID] => 157

[category_count] => 4440

[category_description] => Electronic Design Automation

[cat_name] => EDA

[category_nicename] => eda

[category_parent] => 0

[is_post] =>

)

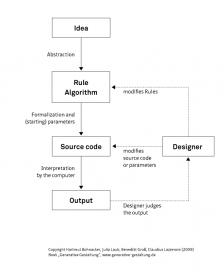

Scanning headlines of technology news every day I was somewhat familiar with the phrase “Generative Design” and even browsed the Wikipedia page to find this informative flow-chart that shows the practice of generative design.

Generative design is an iterative design process that involves a program that will generate… Read More

Intelligence as in the term artificial intelligence (AI) involves learning or training, depending on which perspective it is viewed from –and it has many nuances. As the basis of most deep learning methods, neural network based learning algorithms have gained usage traction, when it was shown that training with deep neural network… Read More

While writing the definitive book on ARM history we could not have imagined a more different exit than the SoftBank acquisition, not even close. It is now very clear why SoftBank acquired ARM for $31B. It is also very clear why alternatives like RISC-V are trending on SemiWiki and will continue to do so, absolutely. No matter what … Read More

One of the unsung heroes of our digital world is the modest voltage converter. Batteries and wired power sources rarely match up with the supply needs for advanced ICs. Leading edge ICs have multiple voltage domains and very often, as in the case of processors, use dynamic voltage scaling to help conserve power. Looking at where … Read More

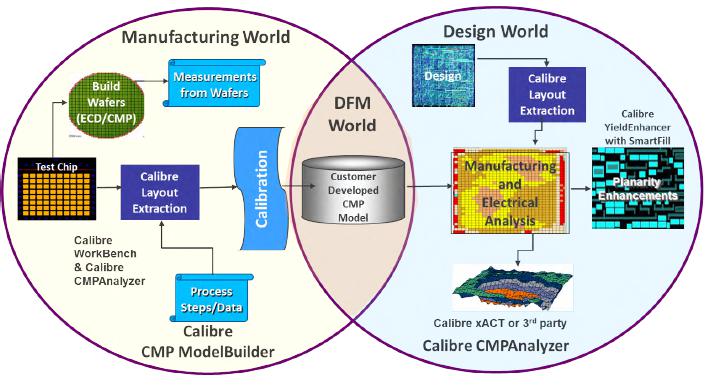

CMP (Chemical Mechanical Planarization or also known as Chemical Mechanical Polishing) is a wafer fabrication step applied generally after a chemical deposition –intended to smoothen and to flatten (planarize) wafer surfaces with the combination of chemical and mechanical forces. Developed at IBM and since its introduction… Read More

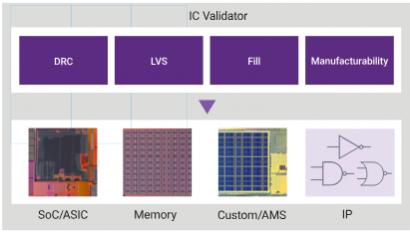

If a picture worths a thousand words, a tapeout quality SoC design with billions of polygons would compose a good book. To proofread this final design transformation format requires a foundry driven DRC/LVS signoff solution that nowadays is becoming more complex with further process scaling and shrinking pitch dimension.

Despite… Read More

One of the more entertaining things I get to observe in the semiconductor ecosystem is competitive customer evaluations of tools and IP. Seriously, this is where the rubber meets the road no matter what the press releases say.

This time it was emulators which is one of the most interesting EDA market segments since there is no dominant… Read More

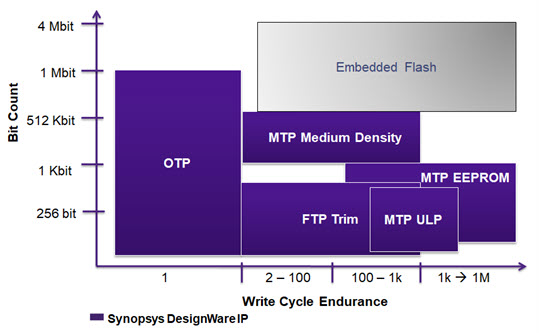

Nobody likes drama. Wait, let me narrow that down a bit. Chip designers really hate drama. They live in a world of risk and uncertainty, a world that tool and IP vendors spend considerable resources trying to make safer and more rational. It’s notable just how ironic that Sidense and Kilopass were duking out patent litigation in the… Read More

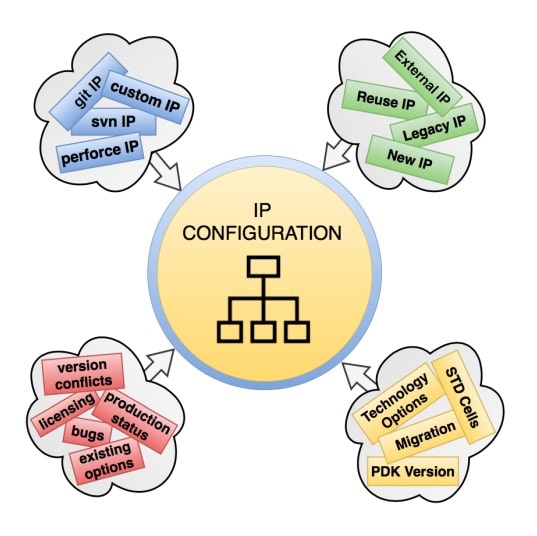

I started designing ICs in 1978 and continued through 1986, and each chip used hierarchy and partitioning but our methodology was totally ad-hoc, and documented on paper, so it was time consuming to make revisions to the chip or train someone else on the history or our chip, let alone re-use any portion of our chips again. Those old,… Read More

At the November 14 Cadence Automotive Summit, Ian Dennison, Senior Group Director, outlined sensor enablement technologies and SoC mixed-signal design solutions, from Virtuoso electrically aware design with high current, high reliability, yield and performance tools and methodologies enabling ADAS/AV sensors for vehicle… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center