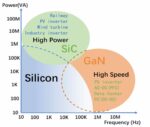

I’ve read articles about power electronics, RF systems and high-frequency applications using SiC and GaN transistors, especially in EVs and chargers, but hadn’t looked into the details of GaN devices. A recent Silvaco webinar proved to be just the format that I needed to learn more about GaN design and optimization. Udita Mittal,… Read More

Electronic Design Automation

MIN PULSE WIDTH (MPW) TIMING CHECK The Silent Timing Trap Lurking in Every Sub-5nm Design

By Zameer Mohammed

This article claims to provide clear key insights of Min Pulse Width (MPW) timing signoff check, proactive closure strategies for faster time-to-market, and effective methods to prevent silicon failures.

Min Pulse Width (MPW) check for timing signoff has become an important design constraint at the sub-5nm… Read More

Scaling Debug Wisdom with Bronco AI

In the business press today I still find a preference for reporting proof-of-concept accomplishments for AI applications: passing a bar exam with a top grade, finding cancerous tissue in X-rays more accurately than junior radiologists, and so on. Back in the day we knew that a proof-of-concept, however appealing, had to be followed… Read More

CEO Interview with David Zhi LuoZhang of Bronco AI

David Zhi LuoZhang is Co-Founder and CEO of Bronco AI with extensive experience in building AI systems for mission-critical high-stakes applications. Previously while at Shield AI, he helped train AI pilots that could beat top human F-15 and F-16 fighter pilots in aerial combat. There, he created techniques to improve ML interpretability… Read More

Synopsys and TSMC Unite to Power the Future of AI and Multi-Die Innovation

In a rapidly evolving semiconductor landscape, where AI demands unprecedented computational power and efficiency, Synopsys has deepened its partnership with TSMC to pioneer advancements in AI-driven designs and multi-die systems. Announced during the TSMC OIP Ecosystem Summit last week, this collaboration leverages … Read More

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit 2025

At the AI Infra Summit 2025, Synopsys showed how artificial intelligence has become inseparable from the process of creating advanced silicon. The company’s message was clear: AI is an end-to-end engine that drives every phase of chip development. Three Synopsys leaders illustrated this from distinct vantage points. Godwin… Read More

Neurosymbolic code generation. Innovation in Verification

Early last year we talked about state space models, a recent advance over large language modeling with some appealing advantages. In this blog we introduce neurosymbolic methods, another advance in foundation technologies, here applied to automated code generation. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano… Read More

Synopsys Collaborates with TSMC to Enable Advanced 2D and 3D Design Solutions

Synopsys has deepened its collaboration with TSMC certifying the Ansys portfolio of simulation and analysis tools for TSMC’s cutting-edge manufacturing processes including N3C, N3P, N2P, and A16. This partnership empowers chip designers to perform precise final checks on designs, targeting applications in AI acceleration,… Read More

The Impact of AI on Semiconductor Startups

At the AI Infra Summit 2025 was a panel conversation that captured the semiconductor industry’s anxieties and hopes. The session, titled “The Impact of AI on Semiconductor Startups,” examined how artificial intelligence is transforming not just what chips can do, but how we design them.

The backdrop is stark. Developing a leading-edge… Read More

Video EP10: An Overview of Mach42’s AI Platform with Brett Larder

In this episode of the Semiconductor Insiders video series, Dan is joined by Brett Larder, co-founder and CTO at March42. Brett explains what March42’s AI technology can do and the benefits of using the platform to quickly analyze designs to find areas that may be out of spec and require more work. He describes the way Mach42… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era