You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At the TERAFAB launch event in Austin on March 21, Elon Musk made a prediction that would have sounded like science fiction a decade ago—and may still: roughly 80 percent of AI compute will eventually move off-planet.

The argument is straightforward once you accept his premises. Earth-based data centers face three hard constraints—land,… Read More

Intel has posted three consecutive years of falling revenue and an $18.76 billion loss in 2024 alone—and the U.S. government has handed it tens of billions of dollars to fix the problem. The government money isn’t fixing the real issue, which isn’t technical. It’s cultural. Intel got slow, political, and risk-averse—the… Read More

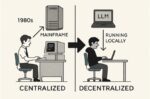

At a workshop in Boston on February 27, something subtle but important happened. Developers sat down in front of a RISC-V laptop, installed Fedora, and ran a local large language model. No simulation. No dev board tethered to a monitor. A laptop.

For more than a decade, RISC-V advocates have promised that the open instruction set… Read More

RVA23 marks a turning point in how mainstream CPUs are expected to scale performance. By making the RISC-V Vector Extension (RVV) mandatory, it elevates structured, explicit parallelism to the same architectural status as scalar execution. Vectors are no longer optional accelerators bolted onto speculation-heavy cores.… Read More

At the 2025 RISC-V Summit, amid debates over cloud scaling and AI cost, DeepComputing CEO Yuning Liang offered a radical view: the future of intelligence isn’t in the cloud at all — it’s already in your pocket. His lunchtime conversation began with iPhones and ended with the death of the operating system. In between, he sketched … Read More

Up to now the RISC-V community has been developing open-source processor implementations to a stage where they can appeal to system designers looking for alternatives to proprietary Arm and x86 cores. Toward this end, two projects have emerged as particularly significant examples of where RISC-V is heading. One is Ara, a vector… Read More

When Morris Chang left Texas Instruments in 1983 to found TSMC, he was not merely starting a new company—he was proposing a new industrial logic. Chang recognized that semiconductor manufacturing had become so capital-intensive that it could no longer survive as just one function inside a vertically integrated company.… Read More

The PC industry is entering its most significant transformation since the debut of the IBM PC in 1981. That original beige box ushered in a new era of productivity, reshaping how corporations and individuals worked, communicated, and created. More than four decades later, the AI PC is emerging as a new category — one that promises… Read More

GlobalFoundries’ (GF) acquisition of MIPS in 2025 wasn’t a nostalgic move to revive a legacy CPU brand. It was a calculated step into one of the most lucrative frontiers in semiconductors: AI, high-performance computing (HPC), and datacenters. As Nvidia, AMD, Intel, and hyperscalers embrace chiplet architectures, GF is betting… Read More

At Embedded World 2025 in Nuremberg, Germany, on March 11, 2025, Yuning Liang, DeepComputing Founder and CEO walked onto the stage with a mischievous smile and a challenge. “What’s the hardest product to make?” he asked rhetorically. “A laptop. It’s bloody hard… but we did it. You can swap the motherboard, you can upgrade, you can’t… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era