We live in an exploding AI world, and this has put pressure on foundries to deliver new products faster than ever before. Any help to accelerate the semiconductor R&D goes a long way to make the life of Fab engineers easier. EDA tools in the TCAD (Technology Computer Aided Design) category are critical for TCAD engineers to accelerating… Read More

Author: Daniel Payne

TCAD Update from Synopsys

Assertion IP (AIP) for Improved Design Verification

Over the years design reuse methodology created a market for Semiconductor IP (SIP), now with formal techniques there’s a need for Assertion IP (AIP). Where each AIP is a reusable and configurable verification component used in hardware design to detect protocol and functional violations in a Design Under Test (DUT). LUBIS … Read More

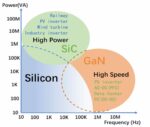

GaN Device Design and Optimization with TCAD

I’ve read articles about power electronics, RF systems and high-frequency applications using SiC and GaN transistors, especially in EVs and chargers, but hadn’t looked into the details of GaN devices. A recent Silvaco webinar proved to be just the format that I needed to learn more about GaN design and optimization. Udita Mittal,… Read More

Simulating Gate-All-Around (GAA) Devices at the Atomic Level

Transistor fabrication has spanned the gamut from planar devices o FinFET to Gate-All-Around (GAA) as silicon dimensions have decreased in the quest for higher density, faster speeds and lower power. Process development engineers use powerful simulation tools to predict and even optimize transistor performance for GAA devices.… Read More

Something New in Analog Test Automation

Digital design engineers have used DFT automation technologies like scan and ATPG for decades now, however, analog blocks embedded within SoCs have historically required that a test engineer write tests that require specialized expertise and that can take man-months to debug. Siemens has a long history in the DFT field, SPICE… Read More

Perforce and Siemens at #62DAC

Wednesday was the last day at #62DAC for me and I attended an Exhibitor Session entitled, Engineering the Semiconductor Digital Thread, which featured Vishal Moondhra, VP Solutions Engineering of Perforce IPLM and Michael Munsey, VP Semiconductor Industry at Siemens Digital Industries. Instead of just talking from slides,… Read More

Moving Beyond RTL at #62DAC

Hardware designers have been using RTL and hardware description languages since the 1980s, yet many attempts at moving beyond RTL have tried to gain a foothold. At the #62DAC event I spent some time with Mike Fingeroff, the Chief High-Level Synthesis Technologist to understand what his company Rise Design Automation is up to. … Read More

Chiplets and Cadence at #62DAC

Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

Software-defined Systems at #62DAC

Modern EVs are prime examples of software-defined systems, so I attended a #62DAC panel session hosted by Siemens to learn more from experts at Collins Aerospace, Arm, AMD and Siemens. Here’s the list of panelists that span several domains, and what follows is my paraphrase of the discussion topics.

Panel Discussion

Q: How does… Read More

Digital Implementation and AI at #62DAC

My first panel discussion at DAC 2025 was all about using AI for digital implementation, as Siemens has a digital implementation tool called Aprisa which has been augmented with AI to produce better results, faster. Panelists were from Samsung, Broadcom, MaxLinear, AWS and Siemens. In the past it could take an SoC design team… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea