At the ES Design West event in San Francisco last week Silvaco’s CTO and EVP of Products, Babak Taheri, gave a presentation titled, “Next Generation SoC Design: From Atoms to Systems”. The time slot for the talk was only 30-minutes which is simply not enough to discuss all the technology Silvaco is providing now. I had not looked closely… Read More

Author: admin

Silvaco Talks Atoms to Systems – Where to Next?

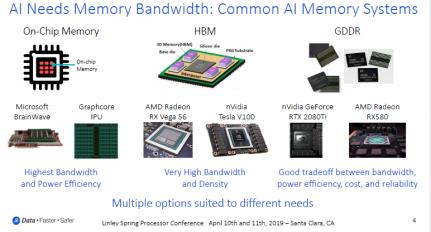

Rambus Take on AI in the Era of Connectivity at Linley Processor Conference

Steven Woo, Fellow and Distinguished Inventor presented at the just concluded Linley Spring Processor Conference a talk about AI in the Era of Connectivity. As he put it, the world is becoming increasingly connected, with a marked surge of digital data, causing a dependence on said data. With the explosion of digital data and AI,… Read More

How to Spice Up Your Library Characterization

It used to be that at the mention of libraries, people would think of foundry PDK deliverables. However, now a host of factors such as automotive thermal requirements, nanometer FinFET processes, near threshold voltages, higher clock rates, high volumes, etc., have dramatically changed library development. These factors … Read More

Spring Forward with AI

The euphoria of NCAA March Madness seems to spill over into the tech world. The epicenter of many tech talks this month spanning from GPU conference, OCP, SNUG to CASPA has evolved around an increased AI endorsement by many companies and its integration into many silicon driven applications. At this year CASPA Spring Symposium,… Read More

SOC security is not a job for general purpose CPUs

Life is full of convenience-security tradeoffs. Sometimes these are explicit, where you get to make an active choice about how secure or insecure you want things to be. Other times we are unaware of the choices we are making, and how risky they are for the convenience provided. If you leave your bike unlocked, you can expect it to be… Read More

The Latest in Parasitic Netlist Reduction and Visualization

The user group events held by EDA companies offer a unique opportunity to hear from designers and CAD engineers who are actually using the EDA tools “in the trenches”. Some user presentations are pretty straightforward – e.g., providing a quality-of-results (QoR) design comparison when invoking a new tool feature added to a recent… Read More

Advanced Materials and New Architectures for AI Applications

Over the past 50 years in our industry, there have been three invariant principles:

- Moore’s Law drives the pace of Si technology scaling

- system memory utilizes MOS devices (for SRAM and DRAM)

- computation relies upon the “von Neumann” architecture

Does the G in GDDR6 stand for Goldilocks?

In the wake of TSMC’s recent Open Innovation Platform event, I spoke to Frank Ferro, Senior Director of Product Management at Rambus. His presentation on advanced memory interfaces for high-performance systems helped to shed some light on the evolution of system memory for leading edge applications. System implementers now… Read More

When it Comes to Process Migration, “Standard Cells” are Anything But

Standard cell library developers are faced with a daunting task when it is time to create a library for a new process node. Porting an existing library can be a big help, but even then, manual modifications to 800 or more cells is still required. Each of those cells has many geometric elements are that affected by new design rules. All… Read More

SPICE Model Generation by Machine Learning

It was 1988 when I got into SPICE (Simulation Program with Integrated Circuit Emphasis)while I was characterizing a 1.5 μm Standard cell library developed by students at my Alma-Mata Furtwangen University in Germany. My professor Dr. Nielinger was not only my advisor he also wrote the first SPICE bible in German language. At that… Read More

TSMC Process Simplification for Advanced Nodes