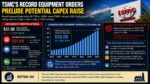

TSMC’s latest Board of Directors capital appropriation announcement may appear mixed on the surface, but a closer look reveals one important conclusion: The company is quietly setting the stage for another potential upward revision to its already aggressive 2026 capital expenditure outlook. The headline figure of $31.3B … Read More

Podcast EP346: How EMD Electronics Bridges the “Lab to Fab” Gap With Ganesh Panaman

Daniel is joined by Ganesh Panaman, the President of Intermolecular Services at EMD Electronics. In his current role, Ganesh is dedicated to accelerating product time-to-market, securing first-mover advantages on disruptive technologies, and actively engaging with the dynamic startup ecosystem in the Silicon Valley. … Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!