The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are bigger versions of what came before and others are new, driven by a new way of designing and assembling semiconductor systems. Synopsys has been at the forefront of innovation to address these challenges and pave the way for future heterogeneous chip designs. The company recently published an informative article on a way to tame yet another challenge for this new design style. Let’s examine how Synopsys addresses the test barrier for heterogeneous integration.

An Overview of the Heterogeneous Design Landscape

There are many dimensions to the challenges of heterogeneous chip design. In a recent post I took a close look at several issues. What was clear is the need for a holistic approach to address these design challenges. All of the items discussed in that post were tied together. A change in one aspect of the design affected others, and so the only way to success was to balance everything in a holistic manner.

Synopsys has developed a strong approach here with a comprehensive suite of solutions to address and balance various design parameters. The list includes architectural design, verification, implementation, and device health. My colleague Kalar Rajendiran also discussed the importance of next generation interconnects in this post. You can learn more about how multi-die packaging is enabling the next generation of AI SoCs and how Synopsys is helping to make this happen.

The Problem with Test for Heterogeneous Chip Design

It seems that this design style increases complexity across many vectors. In the new Synopsys article, advanced testing methodologies are discussed through the lens of needed improvements in automatic test equipment (ATE) to maintain signal integrity, accuracy, and performance.

The article points out that, in the heterogeneous design world structural testing of devices requires high-bandwidth test data interfaces for at-speed testing, to confirm truly known-good devices (KGDs) and to achieve high test coverage and a low DPPM number in a reasonable timeframe. The piece points out that ensuring the highest test coverage for individual chiplets is crucial, before integrating them into complex 2.5D or 3D packages, to prevent yield fallout once they are combined with other chiplets in a complete package.

The article goes on to discuss the number of patterns required to test complex new devices. The patterns have increased significantly, and this is coupled with the fact that there are a limited number of general-purpose IO (GPIO) pins to perform the tests. Furthermore, GPIO speed restricts test data throughput, reducing overall coverage to test advanced designs efficiently. Though the conventional high-speed I/O protocol (PCIe/USB) satisfies the bandwidth requirements, it requires expensive hardware to set up.

Digging a bit deeper, in scenarios where the number of IO pins is limited, the bottleneck often lies in validation time, which extends the product development cycle and significantly increases the test costs. And the limited availability of high-band width test access ports, especially in multi-die design, highlights the need for a new kind of IO. One that can operate at much higher speeds than GPIO but adds no additional hardware components or complex protocol support on the initialization/calibration sequence, while maintaining signal integrity for the latest manufacturing processes.

How Synopsys Addresses the Test Barrier

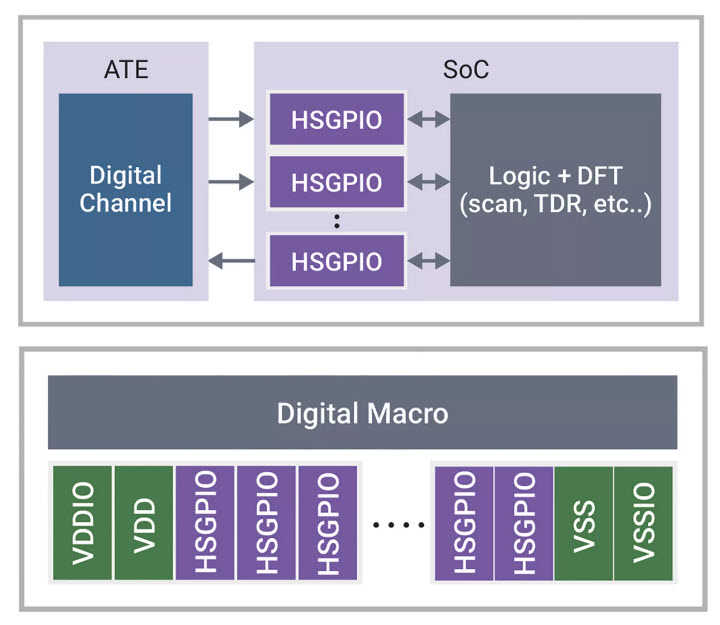

The Synopsys article describes another well designed, holistic approach to the problem. Synopsys High-Speed Test GPIOs (HSGPIO) are optimally designed to meet high-speed test requirements. This versatile offering ensures that single IOs can be multiplexed based on their usage as test ports during manufacturability, performing high-speed clock observation during debug and configurable to GPIO during production, making them unique in the industry in supporting comprehensive test needs.

The article provides a comprehensive overview of the Synopsys solution that includes a detailed discussion of:

- The benefits of high-speed test IO for simplified and reliable testing

- How to enhance IO performance and optimizing power with multiple modes

The graphic at the top of this post illustrates where the Synopsys HSGPIO fits.

If you are planning to utilize heterogeneous design for your next project, the new article from Synopsys is a must-read. Don’t get caught at the end of a complex design process with test headaches. You can access your copy of Synopsys Test IO to address the High-Performance Efficient Data Transmission and Testing requirements for HPC & AI Applications here. And that’s how Synopsys addresses the test barrier for heterogeneous integration.

Also Read:

SNUG 2025: A Watershed Moment for EDA – Part 2

Automotive Functional Safety (FuSa) Challenges

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.