The user group events held by EDA companies offer a unique opportunity to hear from designers and CAD engineers who are actually using the EDA tools “in the trenches”. Some user presentations are pretty straightforward – e.g., providing a quality-of-results (QoR) design comparison when invoking a new tool feature added to a recent release update. Occasionally, a user will convey to the audience an exuberant enthusiasm, describing how a tool enabled new capabilities that changed their methodology – those presentations are especially memorable.

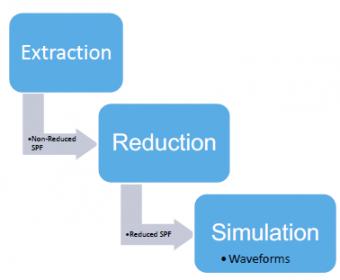

At the recent Silvaco Users Global Event, or SURGE (link), I had the pleasure of attending such a user presentation. The topic was parasitic reduction and netlist qualification – a crucial flow step in the management of signoff electrical and timing analysis. Parasitic netlist reduction is critical to addressing the tradeoff between results accuracy and flow throughput.

Parasitic netlist reduction is somewhat unique, in that it is one of the few steps for which a (best-of-breed) point tool solution is preferred.

Whereas the distinctions between logic synthesis and physical design flows are blurring, and implementation-level timing-noise-power co-optimizations utilize a common data model, parasitic netlists utilize industry-standard file representations – i.e., DSPF, SPEF. Whereas the blended flows require the selection of a broad “platform” of tools from a large EDA vendor, parasitic netlist optimization need not be bound to a specific platform. In that vein, the SURGE user presentation (representing a large semiconductor design company) highlighted how they had integrated the Silvaco Jivaro netlist reduction and Visa netlist visualization tools into their design methodology.

The presentation began with a brief review of parasitic extraction challenges from Jean-Pierre Goujon, AE Manage at Silvaco. “The advanced process technology nodes are resulting in a tremendous increase in the size of extracted netlists that are becoming unmanageable for subsequent signoff analysis flows. Netlist reduction is mandatory.”

Jean-Pierre described some of the unique features required of a reduction tool, including:

- selective reduction: the magnitude of the netlist reduction versus post-reduction accuracy may need to be applied differently on selected nets or hierarchical subckts

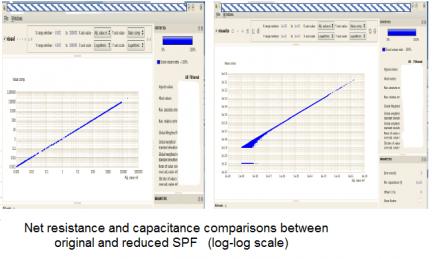

- accuracy feedback: comparisons of pre- and post-reduction net topologies for equivalent (point-to-point) R, Ceff, delay are required; also, methods are needed to detect anomalous R and C data, perhaps related to opens/shorts in the original netlist)

- “full custom” extraction netlist reduction options

The netlists associated with full custom extraction results in tremendous data volume, compared to cell-based interconnect extraction. Intelligent algorithms for (multiple, parallel) active device reduction are required – more on that shortly.

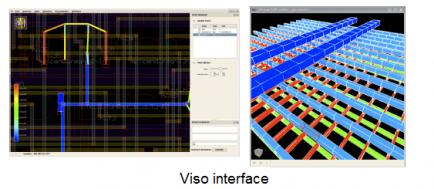

- visualization: a means of visualizing the extraction netlist is needed for debug

Jean-Pierre’s overview was followed by the user perspective. Some of the user highlights were:

“We worked close with Silvaco developers to identify (custom) extracted topologies where aggressive reduction optimizations could be applied. Decoupling capacitors, dummy transistors, and multi-fingered devices are prevalent in custom layouts in advanced nodes, and contribute greatly to the netlist data volume. Unique merging algorithms were used, while maintaining the overall accuracy.”

“There are certainly ‘built-in’ reduction features of commercial extraction tools – yet, we found they did not provide the accuracy versus netlist size targets we were seeking. There were significant net RC differences.”

“And, the (reduced) netlist netnames were impossible to interpret – we used Viso just to try to visualize the topology that was present.”

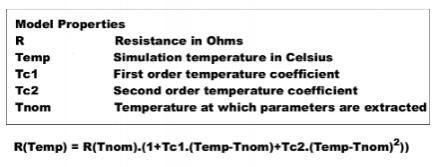

“Our (custom) extracted netlists include resistive elements with Tc1 and Tc2 temperature coefficients – Jivaro correctly managed temperature-sensitive netlists during reduction.”

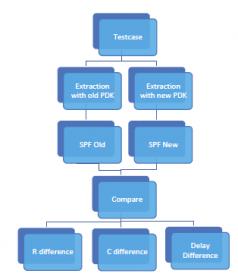

“A key feature to us is the capability to compare extracted netlists (for the same layout). We are designing in advanced process nodes, where the PDK collateral is evolving. Designers need to be able to quickly determine and visualize the extraction differences between PDK releases. The same applies to the evaluation of parasitic differences for extraction at different corners.”

The user’s enthusiasm for the application of Jivaro and Viso into their extraction flow was evident.

He ended with the comment,“By the way, I also want to say that the support from the Silvaco AE team as we were integrating the reduction tools into our flows was excellent.” You don’t often hear that sentiment expressed at these user group events.

-chipguy

Share this post via:

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.