Last week at #54DAC there was a talk by Michael Yu from the CAD group of Oracle who discussed how they designed their latest generation of SPARC chips, with an emphasis on the reliability simulations. The three features of the latest SPARC family of chips are:

- Security in silicon

- SQL in silicon

- World’s fastest microprocessor

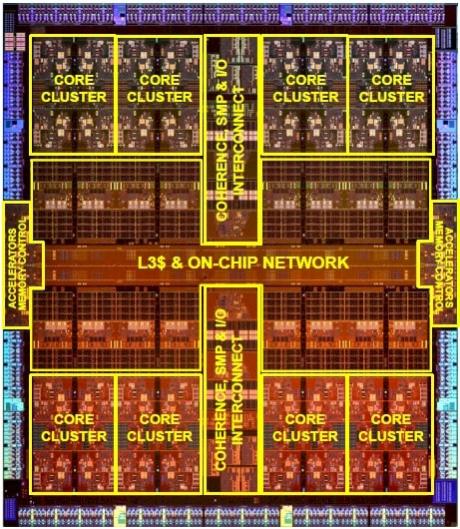

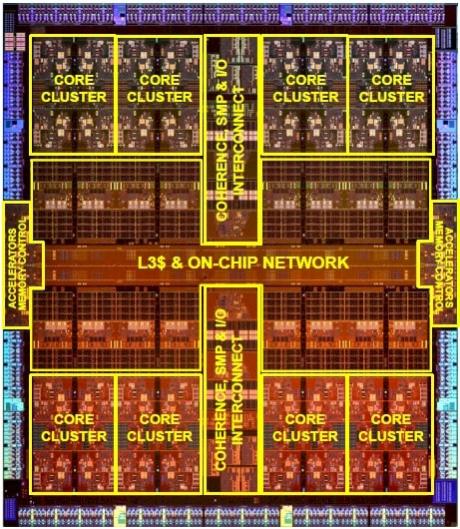

The SPARC S7 is their most recent chip with 8 cores, 8 threads per core, clocked at 4.27GH, built in20nm, and it has 8 FP units per processor. Here’s a chip photo of the related chip called the M7 with over 10 billion transistors:

Source: NextPlatform.com

Designing with 20nm FinFET presented several simulation challenges:

- BSIM CMG device models

- Large number of parasitics

- Poly On Diffusion Edge devices (PODE)

- Coupling effects between layers

- Reliability (self-heating, aging, IR Drops)

The circuit simulation of choice at Oracle is SmartSpicefrom Silvaco and it was used for:

- Standard cell characterization

- Statistical and yield analysis

- Power and signal grid analysis

- Electrical rule check

- EM and IR drop analysis

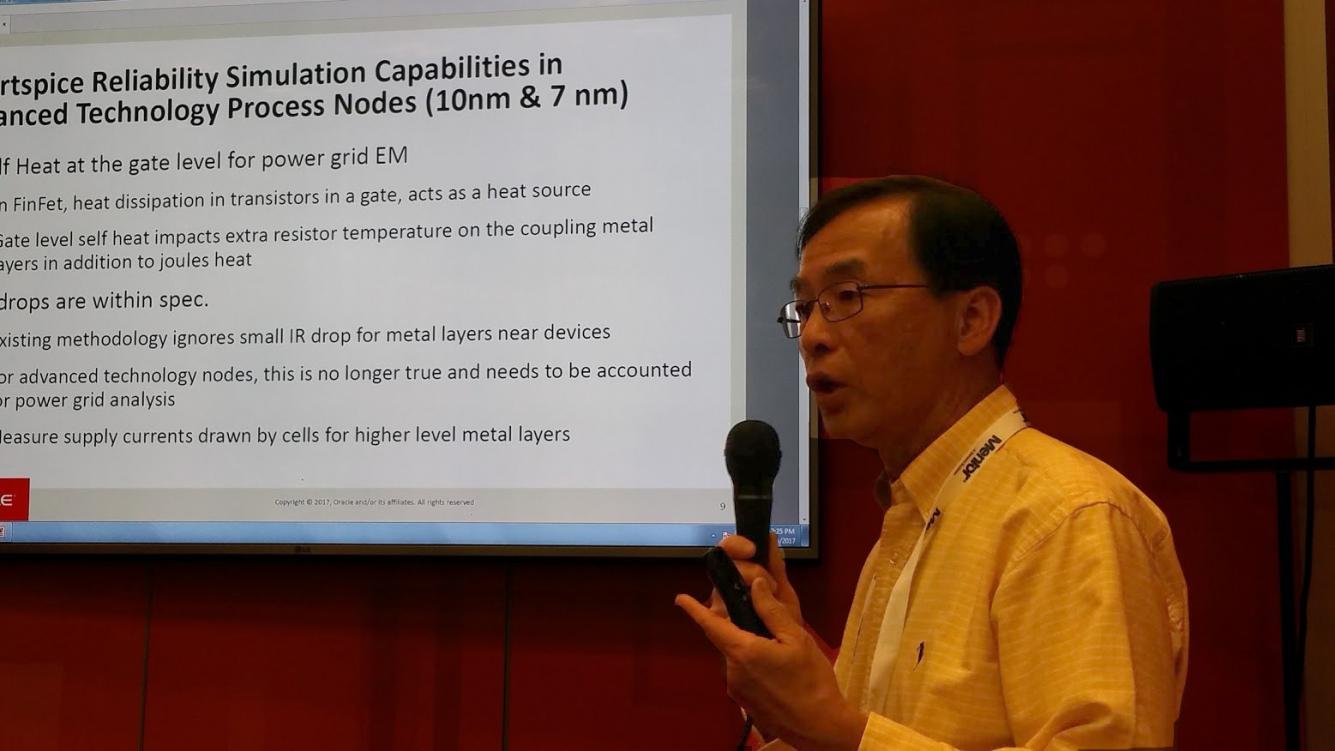

Michael Yu, CAD group of Oracle

Useful features cited were support of multi-threading, save/restore and fast modes. Self heating was a design concern because it impacts device reliability and shows up as gate level effects.IR drop analysis was performed to keep the chip operating within specs, and they measured all current near devices during power grid (PG) analysis.

Related blog – SPICE Circuit Simulator Gets a Jolt

The CAD group at Oracle made use of the SmartSpice API enabling them to analyze data from circuit simulation runs, or even dynamically change values. They used power numbers from each cell, partitioned the netlist, then analyzed power per partition in order to create an accurate top level power number for the chip. This Oracle specific power flow using the SmartSpice API produced power results that were within 5% of full SPICE results, and was also used on SRAM designs in close collaboration with Silvaco.

Another user of the SmartSpice API was to enable a mixed-mode simulation with timing tools used at Oracle.

Finally, having a Silvaco engineer on-site at times would aid in debugging any simulation or API integration issues.

Related blog – SIlvaco at the TSMC 2014 Open Innovation Platform

Q&A

Q: Have you tried using SmartSpice Pro?

A: Not yet, but we have plans to evaluate it.

Q: Can you compare the run times of SmartSpice with any other SPICE tool?

A: Not really.

Q: What are you using for waveform viewing?

A: Mostly we use text viewing for our reports, and some graphical viewing.

Q: Where do your netlists come from?

A: W use an extraction tool from another EDA vendor.

Q: Which foundry was the M7 chip produced at?

A: It was fabricated at TSMC in their 20nm process node.

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.