We blog a lot about Moore’s Law, and even “More than Moore” where 3D integration of ICs and systems are used to get lower product costs. One big challenge with 3D integration of ICs is that most EDA software was really intended only for abstracting at 2D or 2.5D structures. Over the past several years there have been new EDA tools developed that do specifically address the 3D nature of new IC design and packaging. If you’re interested in 3D ICs then consider attending a webinar from Silvaco on Thursday, October 22nd to get some new insight for two specific aspects: Partitioning and DRC for 3D systems and ICs.If you’re an IC engineer or manager looking for better ways to implement 3D designs and analyze, then here’s a summary of what to expect:

- Entry barrier: Difficulties facing 3D ICs and heterogeneous designers.

- EDA Concept: Rationale behind the novel 3D space partitioning software and its integration with the 3D DRC tool

- Design targets: Concept of weighted formulated design penalties

- Design conflicts: Co-optimization of multi-physics criteria

- Speed: High abstraction level for very fast simulations of complex orthogonal design criteria

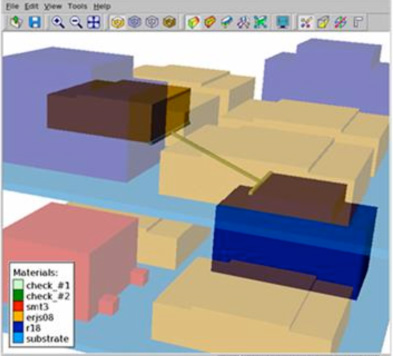

- Manufacturability: How the DRC violations in 3D space can be easily visualized and corrected

- Case studies – 3D partitioning: How to obtain an optimal partitioning and placement of the blocks composing a 3D system in very short time

- Case studies – 3D DRC: how to apply DRC checks in 3D space to feed subsequent full routing and final verification using traditional functional simulators

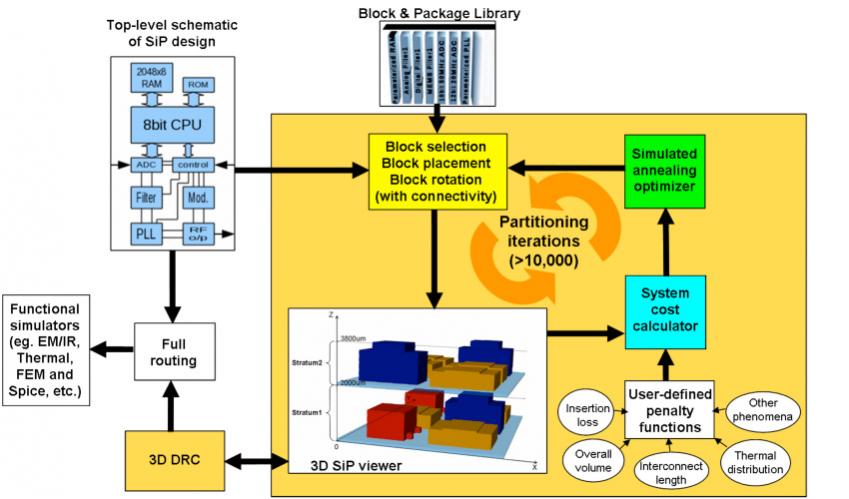

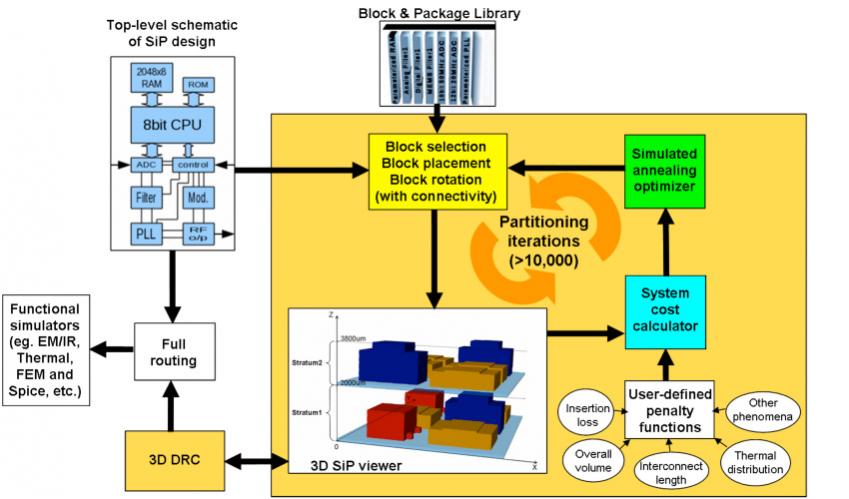

Let me start by showing you a 3D design flow prototype: In the upper-left corner is our top-level schematic of a SiP (System in Package) design. On the top is the block and package library, so the challenge is to figure out how to place and partition each block in a 3D design efficiently and that meets cost goals. Inside the gold box is where all of the partitioning iterations are performed automatically, while giving you feedback about the costs of building each 3D instance.In the lower left is the 3D DRC function, where you would find out if your selected 3D design passes all of the Design Rule Checks for manufacturing.

In the upper-left corner is our top-level schematic of a SiP (System in Package) design. On the top is the block and package library, so the challenge is to figure out how to place and partition each block in a 3D design efficiently and that meets cost goals. Inside the gold box is where all of the partitioning iterations are performed automatically, while giving you feedback about the costs of building each 3D instance.In the lower left is the 3D DRC function, where you would find out if your selected 3D design passes all of the Design Rule Checks for manufacturing. 3D DRC ViolationsThis webinar is presented by Stefano Pettazzi who earned his MS degree in EE from the University of Pavia, Italy. Stefano has been with Silvaco since 2012 and has 15 years experience with both EDA and microelectronics companies. The webinar runs from 4PM to 5PM (BST) and registration is required. If you live in a different timezone, it’s still OK to register for this webinar and then receive an email link to the archived video so that you can view it a more convenient time.Related:

3D DRC ViolationsThis webinar is presented by Stefano Pettazzi who earned his MS degree in EE from the University of Pavia, Italy. Stefano has been with Silvaco since 2012 and has 15 years experience with both EDA and microelectronics companies. The webinar runs from 4PM to 5PM (BST) and registration is required. If you live in a different timezone, it’s still OK to register for this webinar and then receive an email link to the archived video so that you can view it a more convenient time.Related:

- Thermal Reliability and Power Integrity for IC Design

- SEMATECH, Silvaco and SRAM

- Silvaco 30 Years Ago

- The Transistor is the Foundation of TCAD to Signoff

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.