SEMATECH has been around for over 20 years, starting in Austin. Today it is in upstate New York which increasingly seems to be the area for semiconductor research with IBM (still doing research although they sold their semiconductor business to GlobalFoundries), GlobalFoundries’ own Fab 8, the College of Nanoscale Science and Engineering (CSNE).

For a couple of years, Silvaco have been working with SEMATECH in creating an environment where advanced CMOS processes and devices can be created and optimized, all within 2D/3D modeling to help reduce the burdensome costs of manufacturing real wafers. Once a simulation methodology has been created then it can be used for design of experiments (DoE) where design variables can be changed and the outcomes examined in detail.

This collaboration is driven by the challenge of getting maximum performance from advanced designs as CMOS scaling continues to 10nm and beyond. One area of increased interest in simulation is that standard rule-based resistance and capacitance extraction may be insufficient for designs in advanced FinFET technologies. FinFETs introduce even more complexity in designs due to the 3 dimensional nature, including coupling within a single device, between devices and between the devices and the local interconnections. Physical 3D field solver based extraction on the cell-level ensures that the designer takes into account coupling effects between the FinFET device and middle-of-line interconnects.

This collaboration is driven by the challenge of getting maximum performance from advanced designs as CMOS scaling continues to 10nm and beyond. One area of increased interest in simulation is that standard rule-based resistance and capacitance extraction may be insufficient for designs in advanced FinFET technologies. FinFETs introduce even more complexity in designs due to the 3 dimensional nature, including coupling within a single device, between devices and between the devices and the local interconnections. Physical 3D field solver based extraction on the cell-level ensures that the designer takes into account coupling effects between the FinFET device and middle-of-line interconnects.

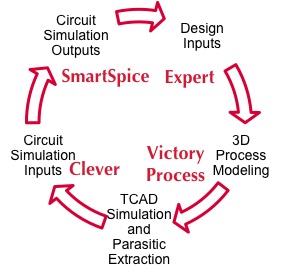

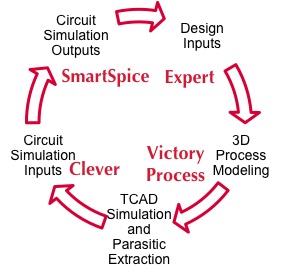

Silvaco approaches this problem via a multi-step process, all using Silvaco’s tools:

[LIST=1]

- a 6T SRAM layout is created in the Silvaco Expert layout editor as a test vehicle

- the 3D structure is created via Victory Process Silvaco’s 3D Process Simulator solution capable of fast geometric structure building as well as detailed physical process modeling.

- Victory Process is layout-based, meaning the 6T SRAM layout is used as an input to define help define the physical structure.

- The resulting 3D structure is passed to Silvaco’s Clever, a 3D physics-based field solver. The active devices are identified and the parasitic the Rs and Cs are extracted with high accuracy, creating a new SRAM netlist which includes added parasitics

- the output netlist is fed into SmartSPICE where it can be paired with compact models for the active transistors and simulated in SPICE

- this creates results at the level that design engineers can analyze

- rinse and repeat via DoE in Silvaco’s Virtual Wafer Fab to understand and optimize the design

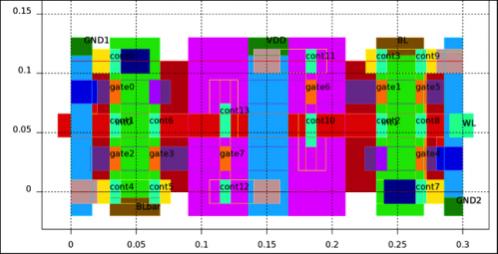

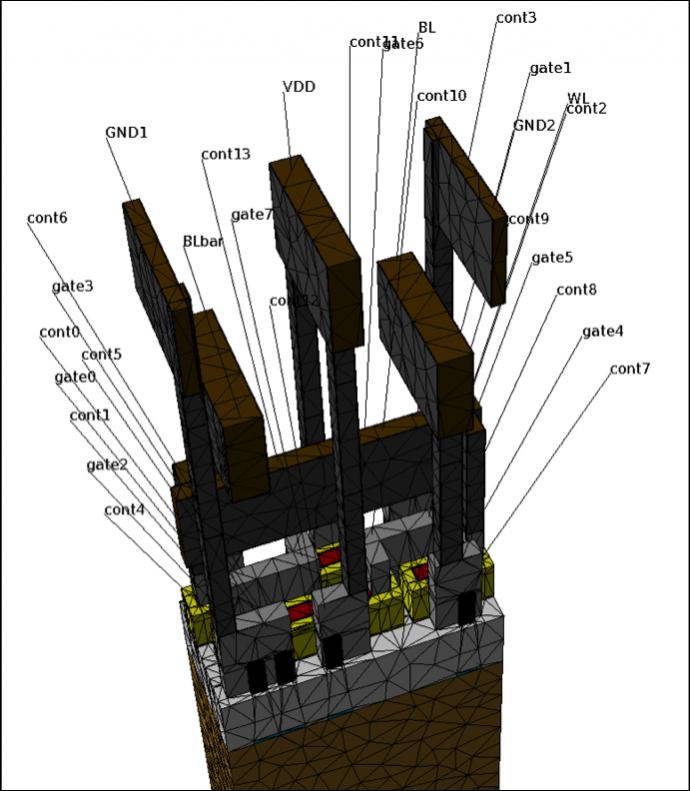

The above diagram shows the layout of the 10nm bitcell. Below is a 3D visualization of the TCAD model of how the bitcell would be built up in the modeled 10nm process.

The above diagram shows the layout of the 10nm bitcell. Below is a 3D visualization of the TCAD model of how the bitcell would be built up in the modeled 10nm process.

Using a design of experiments feedback approach allows study of how design choices impact cell circuit performance and allow optimization to understand and minimize impact of parasitic RCs. Furthermore, due to the direct link between the 3D structure and RC-extracted SPICE simulation, it is possible to analyze the impact of structural variation due to process or layout on performance to better understand margining requirements.

Using a design of experiments feedback approach allows study of how design choices impact cell circuit performance and allow optimization to understand and minimize impact of parasitic RCs. Furthermore, due to the direct link between the 3D structure and RC-extracted SPICE simulation, it is possible to analyze the impact of structural variation due to process or layout on performance to better understand margining requirements.

In addition to the RC extraction investigation, Silvaco has also collaborated with SEMATCH in other related areas.

- thermo-mechanical simulation of through silicon vias (TSVs)

- Detailed 3D TCAD Device simulation, modeling electrical and stress performance of 14nm FinFETs

For full details see Silvaco at at TSMC’s OIP on September 17th

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

There are no comments yet.

You must register or log in to view/post comments.