I’ve been using SPICE circuit simulators since 1978, both internally and commercially developed, and a lot has changed since the early days where netlists were simulated in batch mode on time-share mainframes. We used to wait overnight for our simulations to complete, and in the morning had to pickup our output results as a thick stack of folded paper, but only if there were no syntax mistakes. If your output was only two pages long, then you had a typo in your netlist. Today, however we have fast workstations and interactive circuit simulation, so finding a typo takes a few seconds.

Silvacohas offered their circuit simulator called SmartSpice for decades now, and in the latest release there are two big improvements that are rather compelling to the circuit designer: parallelism and hierarchy.

Parallelism

The classic UC Berkeley SPICE Circuit Simulator and many derivative simulators would read in a netlist and then build a single, large matrix to solve for node voltages and branch currents. This simulation method is well understood, produces accurate results, although the run times can be lengthy because of all the floating point math calculations.

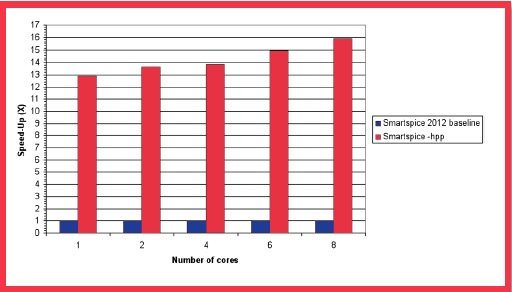

SmartSpice has introduced a new command line option, called “-hpp”, that will instead automatically break up the single, large matrix into multiple smaller matrices that can be run in parallel on different cores, thus speeding up the simulation time dramatically. The good news for design engineers is that this step is fully automated, you don’t have to identify partitions or make any decisions, just use the new command line option and start getting results back faster. The following chart shows that you can expect up to a 14X faster results when running on 4 cores.

Even with a single core, there’s up to 13X speed improvement versus a baseline of SmartSpice 2012.

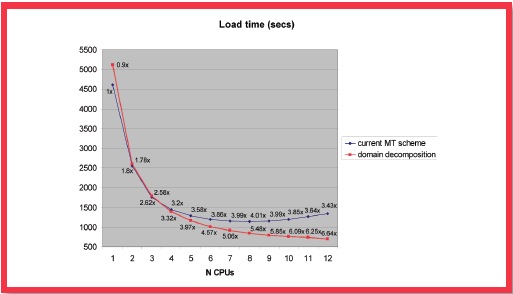

Improvements have also been made to shorten the time that it takes to load in large netlists with millions of elements by using a domain decomposition method. Here’s a chart showing that you can reduce load times by almost 10X when using 12 cores and the new Domain Decomposition Solver (DDS):

Hierarchy

Designers of DRAM, SRAM, Flash and TFT circuits often use massive amounts of hierarchy in their netlists. SmartSpice will now take advantage of that hierarchy with the DDS option and an isomorphism option, so that during circuit simulation the hierarchical cells can share their results instead of all being simulated individually.

Summary

Silvaco has kept up with the times by adding new options to SmartSpice that speed up circuit simulation run times and expand the capacity. The benefits are that you can now run more simulations in the same amount of time, providing you more confidence that first silicon will be correct.

lang: en_US

Share this post via:

![SILVACO 051525 Webinar 400x400 v2[62]](https://semiwiki.com/wp-content/uploads/2025/04/SILVACO_051525_Webinar_400x400_v262.jpg)

Comments

0 Replies to “SPICE Circuit Simulator Gets a Jolt”

You must register or log in to view/post comments.