Overview

Processor IP refers to pre-designed, licensable CPU or processing core designs used in System-on-Chip (SoC) development. These IP cores are integrated into semiconductor designs and are responsible for executing instructions, controlling hardware, and performing computations.

Processor IP enables companies to build custom chips without designing a CPU from scratch, reducing development time and cost while allowing scalability across different markets and applications.

📦 Types of Processor IP

| Category | Description | Examples |

|---|---|---|

| CPU IP | General-purpose processors for control and application execution | Arm Cortex-A/M/R, RISC-V (SiFive, Andes), Synopsys ARC |

| DSP IP | Specialized in real-time signal processing (MAC-heavy workloads) | CEVA-X, Cadence Tensilica, Arm Helium |

| GPU IP | For graphics and compute tasks (2D/3D rendering, shaders) | Arm Mali, Imagination PowerVR |

| AI/ML IP | Neural processing units (NPUs), optimized for inference | Arm Ethos, CEVA NeuPro, Cadence DNA |

| Secure Processor IP | Hardware root of trust, crypto operations | OpenTitan, Secure-IC, PQShield |

| Embedded Controllers | Lightweight cores for control functions | Arm Cortex-M0/M3, ARC EM, RISC-V RV32 |

🛠️ Key Features

| Feature | Purpose |

|---|---|

| ISA (Instruction Set Architecture) | Defines how software communicates with hardware (e.g., Arm, RISC-V) |

| Pipeline Architecture | Controls throughput and instruction execution stages |

| Multicore & Multithreading | Improves parallelism and performance |

| Cache Hierarchy | L1, L2, L3 caches for memory access optimization |

| Debug and Trace | Interfaces for JTAG, breakpoints, real-time monitoring |

| Security Extensions | TrustZone (Arm), PMP (RISC-V), Secure Boot |

| Custom Extensions | Application-specific instructions (e.g., AI, DSP) |

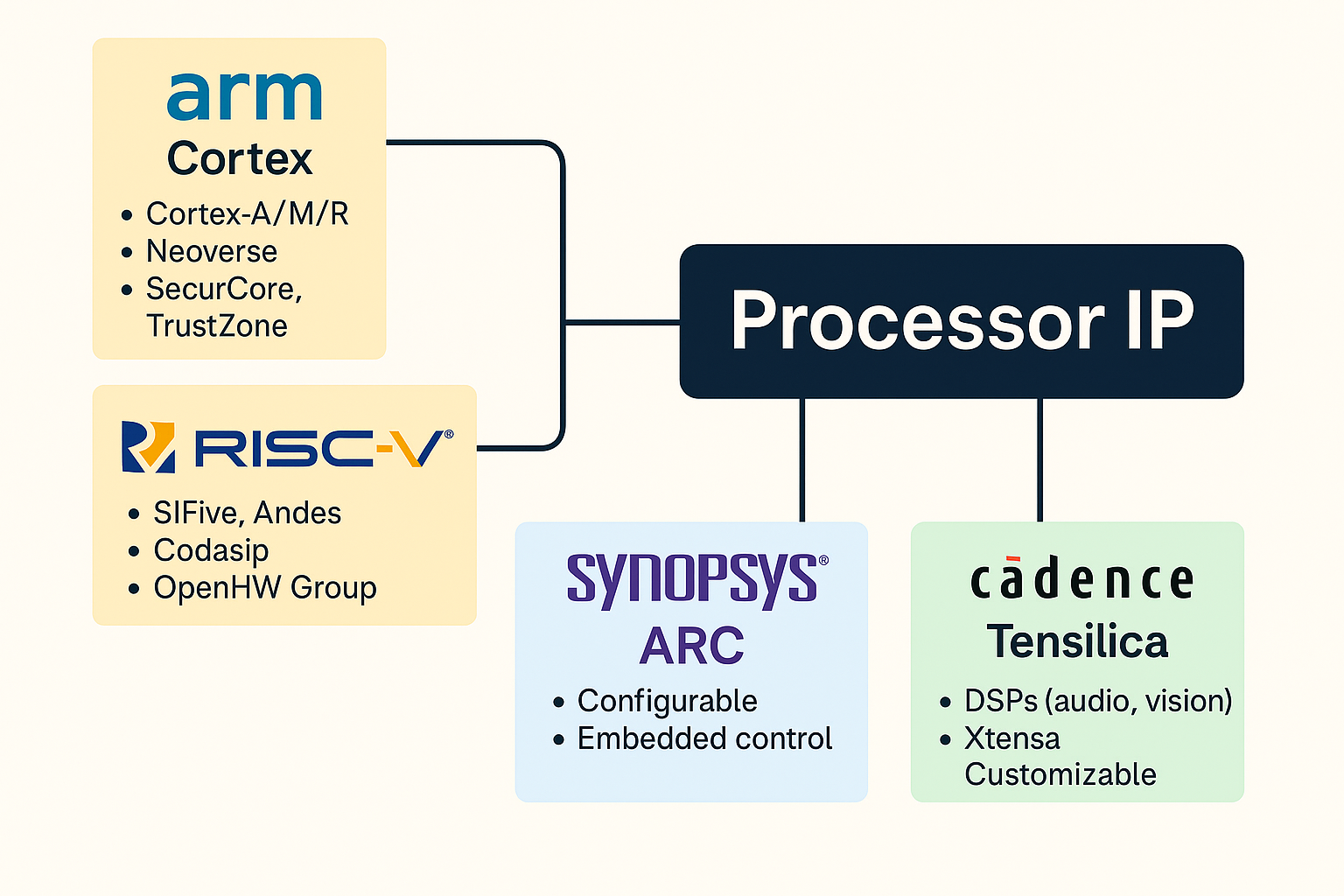

🧮 Common Architectures and Providers

🔹 Arm

-

Cortex-A: Application processors (smartphones, tablets)

-

Cortex-R: Real-time processors (automotive, storage)

-

Cortex-M: Microcontrollers for IoT/embedded (e.g., M0, M3, M7)

-

Neoverse: Server/data center CPUs

-

SecurCore / TrustZone: Secure element processors

🔹 RISC-V

-

Open-source ISA with multiple providers:

-

SiFive – Performance and embedded RISC-V cores

-

Andes Technology – Compact and DSP-extended cores

-

Codasip – Customizable RISC-V cores with compiler toolchains

-

OpenHW Group – Open-source RISC-V cores (e.g., CV32E)

-

🔹 Synopsys ARC

-

Configurable 32-bit/64-bit cores optimized for embedded control and DSP

-

Targeted at audio, voice, sensor processing

🔹 Cadence Tensilica

-

HiFi DSPs: Audio, voice, soundbar, ANC, hearing aids

-

Vision DSPs: Imaging, vision, SLAM, ML

🔹 CEVA

-

Wireless (CEVA-X), vision, and AI cores (SensPro, NeuPro)

-

Strong in Bluetooth, 5G, sensor fusion

🔹 Imagination Technologies

-

MIPS (legacy CPU line) and Catapult RISC-V CPUs

-

Also offers GPU and AI cores

📈 Market Adoption

Processor IP is used in nearly every custom SoC across industries:

| Industry | Application |

|---|---|

| Mobile | Application CPUs (Arm Cortex-A), audio (Tensilica, CEVA), camera |

| IoT | Microcontrollers (Cortex-M, RISC-V), BLE radios |

| Automotive | Safety controllers, ADAS compute (Cortex-R, DSPs) |

| Networking | Packet processing (ARC, RISC-V), secure routing |

| AI/ML Edge | DSP+NPU combo processors for inference |

| Storage | SSD controllers (ARC, Cortex-R) |

| Wearables | Compact power-efficient CPUs (M0, RISC-V RV32) |

💡 Licensing Models

| Model | Description |

|---|---|

| Upfront license + royalties | Pay for use, plus per-chip royalty (standard model) |

| Subscription (SaaS IP) | Newer model from Arm, others (for early startups) |

| Royalty-free (open source) | RISC-V under permissive license (e.g., Apache 2.0) |

| Single-use or multiproject | Limits use to one SoC or multiple derivatives |

🧭 Design and Integration Tools

Processor IPs are typically bundled with:

-

RTL code (for soft cores) or GDSII (for hard macros)

-

Toolchains: GCC/LLVM-based compilers, IDEs, JTAG support

-

SoC integration kits: AMBA AXI/AHB bus interfaces, debug ports

-

Models: ISS (Instruction Set Simulator), Cycle-accurate models

-

SDKs and BSPs: For OS booting, HALs, and reference software

🔒 Secure and Safety IP Features

| Feature | Use Case |

|---|---|

| Secure Boot ROM | Authentication at reset |

| TrustZone (Arm) | Partition secure/non-secure domains |

| RISC-V PMP (Physical Memory Protection) | Hardware memory access control |

| Safety ISO 26262 ASIL-D support | Automotive use |

| Hardware crypto engines | Secure data and communications |

Things From Intel 10K That Make You Go …. Hmmmm