The MIPI Alliance (Mobile Industry Processor Interface Alliance) is a global, non-profit industry consortium that develops open interface specifications for mobile and mobile-influenced industries. These specifications standardize the interfaces between components in devices such as smartphones, tablets, cameras, AR/VR headsets, automobiles, IoT devices, and increasingly, laptops and embedded systems.

Founded in 2003, MIPI has become a central force in enabling low-power, high-speed connectivity between cameras, displays, sensors, and processors in modern electronics.

📜 Overview

-

Founded: 2003

-

Type: Non-profit, open membership industry consortium

-

Headquarters: United States

-

Membership: 400+ member companies worldwide

-

Focus: Standardizing high-performance, low-power interfaces for mobile and adjacent markets

🎯 Mission and Goals

-

Develop interface specifications that reduce integration complexity, power consumption, and cost.

-

Promote interoperability across a broad ecosystem of chips, devices, and platforms.

-

Enable scalability across various verticals including mobile, automotive, industrial, medical, and IoT.

🧩 Key Specifications and Protocols

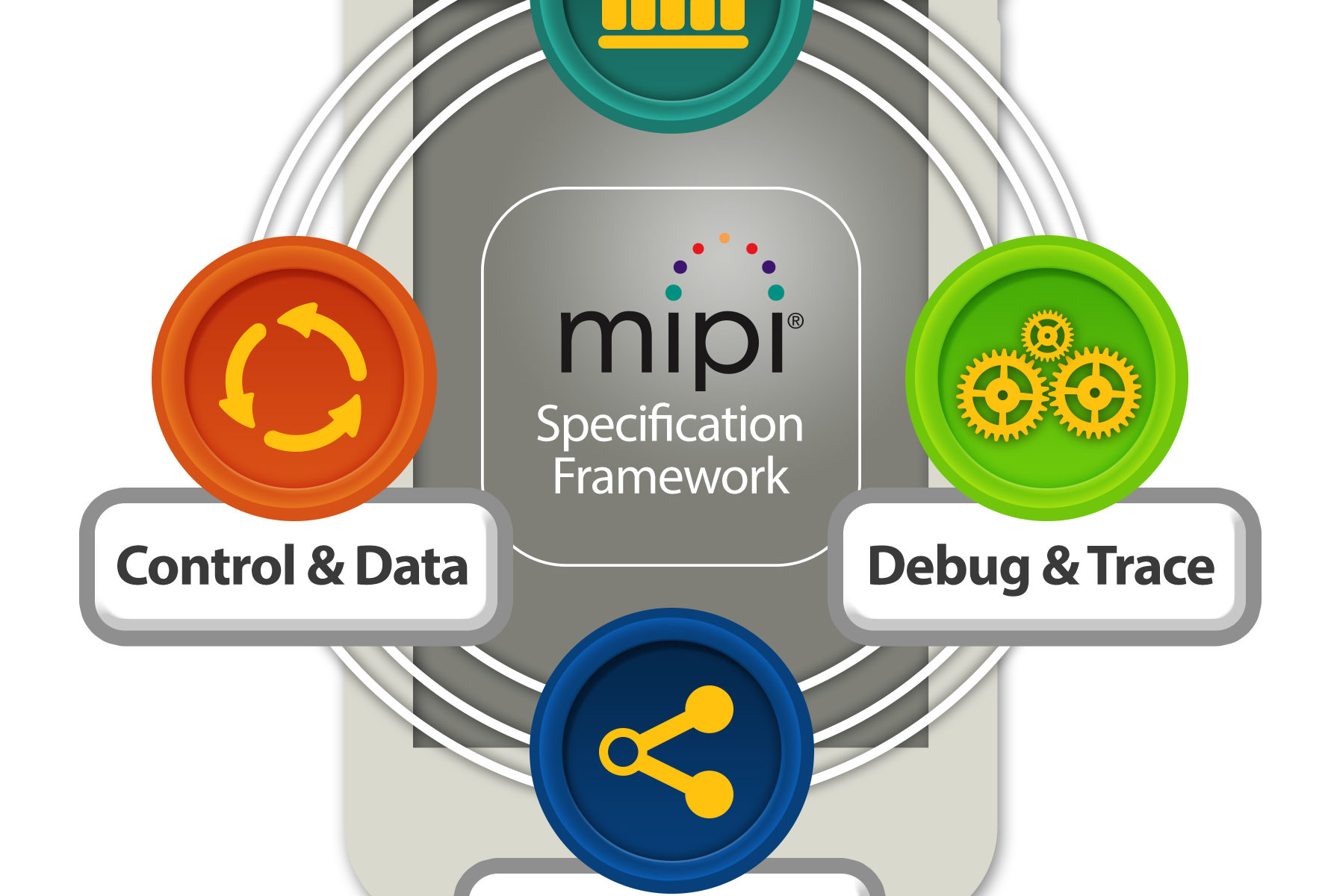

MIPI develops over 50 interface specifications. These are grouped into several categories:

1. Camera Interfaces

-

MIPI CSI-2 (Camera Serial Interface)

-

Most widely used camera interface in mobile and embedded devices

-

Supports high-resolution image sensors and video capture

-

Versions up to CSI-2 v4.0 (2021) support multi-gigabit speeds and RAW image formats

-

2. Display Interfaces

-

MIPI DSI/DSI-2 (Display Serial Interface)

-

Connects processors to displays (smartphones, tablets, AR/VR)

-

DSI-2 supports VESA DSC compression and variable refresh rates

-

Common in AMOLED, LCD, and microLED displays

-

3. PHY Layers (Physical Layer Standards)

-

MIPI D-PHY: Used with CSI-2 and DSI; supports up to 4.5 Gbps/lane

-

MIPI C-PHY: Alternative to D-PHY; better signal integrity over fewer pins

-

MIPI M-PHY: Used in high-performance applications like UFS and PCIe

-

MIPI A-PHY: Automotive PHY for long-reach (up to 15 meters) high-speed connections

4. Chip-to-Chip Interfaces

-

MIPI UniPro: Transport layer protocol; used in UFS (Universal Flash Storage)

-

MIPI I3C: Successor to I2C; more efficient for connecting sensors

-

MIPI SLIMbus: Audio and control interface in mobile systems

-

MIPI SoundWire: Simplifies audio component connectivity

5. Automotive

-

MIPI A-PHY: Robust, long-reach (15+ meter) automotive serializer-deserializer (SerDes) interface

-

Built for cameras, radar, LiDAR, displays in ADAS and autonomous driving

-

Compatible with CSI-2 and DSI protocols

🚗 Industry Applications

| Market | Use of MIPI Specifications |

|---|---|

| Mobile Devices | Cameras (CSI-2), Displays (DSI), Audio (SoundWire), Memory (UFS via M-PHY), Sensors (I3C) |

| Automotive | In-vehicle cameras, radar, and displays using CSI-2/DSI over A-PHY |

| AR/VR | Low-latency, high-resolution camera and display interfaces |

| IoT/Edge | Efficient sensor interfacing using I3C, reduced pin count |

| Wearables | Power-efficient and compact form factors using CSI-2, D-PHY |

| Laptops/Tablets | Integration of mobile-grade cameras and sensors using MIPI |

📶 Technology Advantages

-

Low Power Consumption

-

High Bandwidth per Lane (up to 32 Gbps with A-PHY and C-PHY)

-

Fewer Pins and Smaller Form Factors

-

Scalable Architecture for Broad Use Cases

-

Robustness for EMI, EMC, and Automotive Safety Standards

📚 Membership and Ecosystem

Member Categories:

-

Promoter Members: Founding and key contributors (e.g., Arm, Intel, Qualcomm, Samsung, STMicroelectronics, Synopsys)

-

Contributors: Help develop specifications

-

Adopters: Use and implement specifications

Member Companies Include:

-

AMD, Apple, Bosch, Intel, MediaTek, NVIDIA, NXP, Sony, Texas Instruments, Synopsys, Cadence, TSMC

🛠️ Compliance and Tools

-

MIPI Alliance does not directly certify products, but encourages self-testing and ecosystem-driven compliance.

-

Test and debug tools provided by:

-

Keysight Technologies

-

Teledyne LeCroy

-

Rohde & Schwarz

-

Cadence and Synopsys (for PHY IP validation)

-

🧱 MIPI IP and Silicon Integration

MIPI standards are implemented in IP blocks licensed by semiconductor IP vendors, and are included in SoC designs through:

-

MIPI PHY IP (D-PHY, C-PHY, A-PHY, M-PHY)

-

Protocol Controllers (CSI-2, DSI-2, I3C)

-

Verification IPs for pre-silicon simulation

-

Bridge and Retimer Chips for automotive and industrial use

🔮 Emerging Trends and Developments

-

MIPI I3C Basic adopted by JEDEC for memory module management

-

A-PHY adoption in automotive ADAS platforms (Mercedes, Tesla, Toyota suppliers)

-

6G and Edge AI driving expansion of CSI-2/DSI-2 into new performance realms

-

MIPI security extensions to protect sensor and display data integrity

-

Standardization with UCIe and chiplet packaging ecosystems

🧾 MIPI vs Other Interface Standards

| Feature | MIPI CSI/DSI | LVDS | HDMI | USB |

|---|---|---|---|---|

| Power | Very low | Moderate | High | Moderate |

| Distance | Short (a few cm) | Medium | Long | Long |

| Use Case | Internal mobile/video links | Industrial display | Consumer AV | General I/O |

| PHY | D-PHY/C-PHY | Differential pairs | TMDS | NRZI/High-Speed Differential |

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!