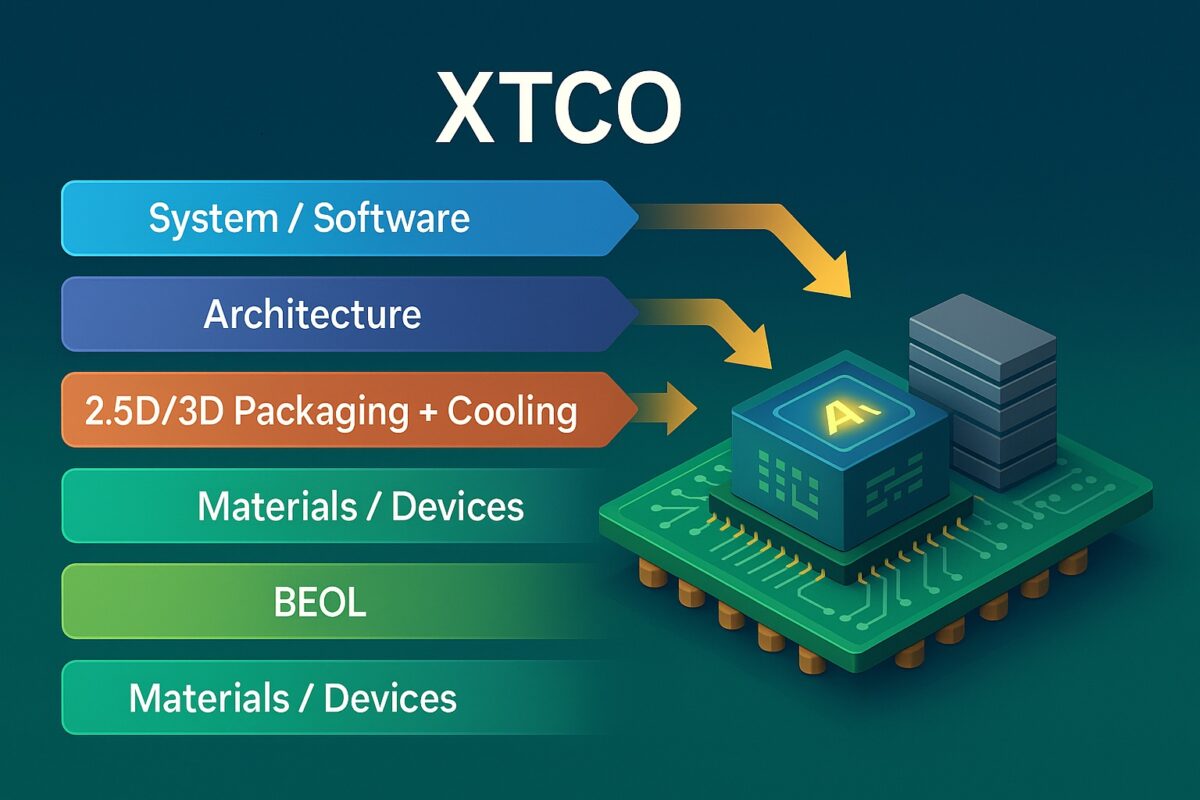

XTCO (Cross-Technology Co-Optimization) is a holistic methodology that coordinates multiple layers of technology and design—devices, interconnect/BEOL, 3D integration & packaging, architecture, and system/software—to deliver target PPAC (performance, power, area, cost) plus reliability and time-to-market. It generalizes prior co-optimization frameworks such as DTCO (design-technology) and STCO (system-technology) into a single, end-to-end stack used to break modern system-scaling bottlenecks.

What XTCO Covers (the stack)

-

Materials & Devices: transistor options (nanosheet, forksheet, CFET), backside power, device reliability.

-

Interconnect/BEOL: RC scaling, via resistance, BEOL materials, BSPDN routing.

-

3D & Packaging: 2.5D/3D chiplets, hybrid bonding, HBM proximity, thermal/mechanical co-design.

-

Architecture & Workloads: partitioning into chiplets, memory hierarchy, fabrics, near-memory compute.

-

System & Software: board/cooling, firmware, compiler/runtime choices that change activity factors and power.

XTCO orchestrates trade-offs across these layers rather than optimizing any one in isolation.

Why XTCO?

-

Post-Dennard era: Gains come from co-design, not just smaller transistors.

-

Chiplet economics: Partitioning and packaging choices now rival node shrinks in impact.

-

Thermal & power limits: Cooling, PDN, and floorplanning must be decided with workload behavior in mind.

-

Predictable delivery: Early techno-economic models steer PPAC and schedule/risk.

Core Loop (typical XTCO workflow)

-

Top-down targets: System KPIs (throughput/latency, power envelopes, cost, reliability).

-

Architectural partitioning: Explore monolithic vs. chiplet graphs; memory/HBM placement.

-

Technology option sets: Devices/BEOL, BSPDN, 3D stack, packaging flows (CoWoS/FO-PLP/Foveros, etc.).

-

Design-space exploration: Multi-physics + EDA models for timing, SI/PI, thermals, yield, cost.

-

Down-selection & prototyping: Close on feasible PPA/thermal/yield corners; de-risk with early vehicles.

-

Sign-off with guardbands: Include variability, aging, supply chain and manufacturability checks.

Key Methods & Models

-

Hierarchical PPACe: Add e (embodied energy/carbon) to PPAC when relevant.

-

Yield & cost coupling: Known-good-die assumptions, compounded yields for 3D/2.5D, COGS vs. throughput.

-

Thermal-electrical co-simulation: PDN + heat-flow + activity traces from real workloads.

-

Interconnect-aware DSE: Fabric topology, reticle/bridge limits, package RDL and via budgets.

Common Deliverables

-

Partition maps (chiplets, HBM stacks, bridges).

-

Techno-economic dashboards (PPACe vs. options).

-

Risk burndown plans (cooling, warpage, alignment, test).

-

Interfaces & standards selections (UCIe, CXL/PCIe) aligned to packaging limits.

Prime Use Cases

-

AI/HPC accelerators: Balance node choice, HBM count/placement, 3D cache, and liquid cooling.

-

Dense edge systems: Co-optimize BSPDN, 3D DRAM proximity, and packaging for size/power limits.

-

Networking & CPO: Optimize SerDes reach, co-packaged optics adjacency, and thermal paths.

Relationship to DTCO/STCO

-

DTCO focuses on design ↔ process for a node.

-

STCO lifts to system ↔ technology trade-offs.

-

XTCO spans cross-layer decisions and programs that coordinate DTCO & STCO with packaging and compute-density roadmaps. (Several research and industry forums now run dedicated XTCO sessions and leadership roles.)

Metrics to Watch

-

PPA & PPACe trajectories across option sets

-

Energy per task / per token (AI), perf/W

-

Thermal density & cooling ΔT, IR-drop margins

-

Compound yield & cost per good system

-

Time-to-market (TtM) vs. risk gates

Typical Challenges

-

Model fidelity vs. exploration speed; aligning EDA/TCAD/packaging tools

-

Data hand-offs between teams (device ↔ package ↔ system) and IP confidentiality

-

Early availability of accurate package/cooling PDKs

-

Supply-chain synchronization across foundry, OSAT, substrate, and cooler vendors

Notable Quotes (unattributed)

-

“XTCO turns isolated optimizations into a contract between device, package, and system.”

-

“In the chiplet era, the package is part of the architecture—XTCO makes that explicit.”

-

“If it isn’t modeled together, it won’t land together—performance, power, thermals, cost.”

-

“You don’t win PPAC; you budget it across layers.”

-

“Workloads are the spec—XTCO starts from software behavior and works down.”

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry