Intro

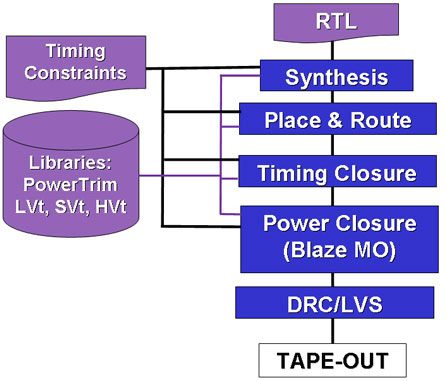

Neal Carney, VP of Marketing at Tela Innovations provided me an update at DAC last week. Their company partnered with TSMC to reduce leakage in IC designs by biasing the gate lengths on your paths that are non-critical to timing.

Notes

Why do this?

– Reduce leakage

– Increase gate lengths on paths with slack

– Recharacterize cells for change channel length, new performance

– Take the output from Primetime for paths with slack

– Our tool also has a timing engine built into it

– Fine grain optimization for leakage optimization

– Our tool does more cell swaps than other tools do

– Can swap multi vt cells as well

– TSMC has four Vt choices, but with gate biasing you have finer control than just swapping Vt

– Gate biasing doesn’t require another mask

– Optimize for: Performance, leakage, costs

– At 28nm the PowerTrim libraries should become more mainstream

– At 40nm, you can bias the gate length to optimize as well

– Another technique for 28nm is to start with 35nm then use gate biasing

– Customers can ask for design services from Tela, or ask TSMC to use PowerTrim

– Customers: LSI Logic, Melanox, undisclosed (over 50 tapeouts so far)

– Gate biasing can make the device go faster (more leakage) or slower (less leakage)

Summary

If you fab with TSMC and want to reduce your leakage currents, then consider the PowerTrim library approach.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center