At DAC in 2011 I visited an EDA company called Silicon Frontline Technology because they offered some 3D field solver tools used to create the highest accuracy netlists that can then be simulated with a SPICE circuit simulator to predict timing, power and IR drop. A recent press release with X-FAB and Silicon Frontline looked interesting so I contacted Thomas Hartung, the VP Marketing and Joerg Doblaski, the team leader of the Design Technology Group at X-FAB to better understand their IC design process and why it required a 3D resistance extractor.

Bios

Thomas Hartung, vice president of marketing at X-FAB Semiconductor Foundries since the late 1990s, leads the company’s worldwide marketing activities. He brings strong technical and marketing expertise to this position at X-FAB, the leading specialty foundry focused on manufacturing silicon wafers for analog-digital integrated circuits. Prior to joining X-FAB, Mr. Hartung served as director of product marketing at Thesys Gesellschaft für Mikroelektronik mbH, where he earlier began his career as a process engineer. He holds a diploma in physics from the Friedrich Schiller University in Jena, Germany.

Thomas Hartung, vice president of marketing at X-FAB Semiconductor Foundries since the late 1990s, leads the company’s worldwide marketing activities. He brings strong technical and marketing expertise to this position at X-FAB, the leading specialty foundry focused on manufacturing silicon wafers for analog-digital integrated circuits. Prior to joining X-FAB, Mr. Hartung served as director of product marketing at Thesys Gesellschaft für Mikroelektronik mbH, where he earlier began his career as a process engineer. He holds a diploma in physics from the Friedrich Schiller University in Jena, Germany.

Jörg Doblaski works as a Senior Engineer at X-FAB Semiconductor Foundries. As leader of Design Technology group, he is responsible for maintenance and improvement of X-FAB’s design flows. He has several years of experience in developing Cadence-based Process Design Kits for both IC5.1 and IC6.1. Before starting his work at X-FAB, he studied electrical engineering at the Technical University of Ilmenau, Germany.

Jörg Doblaski works as a Senior Engineer at X-FAB Semiconductor Foundries. As leader of Design Technology group, he is responsible for maintenance and improvement of X-FAB’s design flows. He has several years of experience in developing Cadence-based Process Design Kits for both IC5.1 and IC6.1. Before starting his work at X-FAB, he studied electrical engineering at the Technical University of Ilmenau, Germany.

Questions

Q: Who are your IC design customers?

A: They are companies doing analog mixed-signal designs, big analog designs, fabless, OEM designers, high voltage, automotive, power management and consumer areas. Our customer chips are in many smart phones and automotive applications.

Q: Why do you need 3D resistance extraction and analysis?

A: For accurate analysis and optimization of Rdson in driver designs our customers needed a new tool, instead of relying on intuition.

Q: How did you choose R3D from Silicon Frontline Technology?

A: At DAC one year ago we met and talked with SFT about their tools and then decided to evaluate R3D. There really aren’t any other EDA companies offering extraction and analysis for driver designs, so we choose R3D.

Q: Pcells are supported for Cadence-based PDKs, how about support for iPDK?

A: As a foundry we support the major PDKs: Cadence (Skill), Synopsys (iPDK – translate from Skill to Python functionality), Mentor, Tanner. Standards are important so iPDK reduces our development effort, we are all for it.

Q: Why was R3D selected?

A: Customers get better first silicon that is optimized because it has been analyzed, they can find and fix issues of current hot spots.

Q: How will X-Fab be more productive after using R3D?

A: We use SFT in our own test chips, and optimize our own primitive devices and for our Pcells. SFT is recommended but not required in customer design flows. We provide the SFT technology files in our PDK.

Q: What size of designs are run with R3D?

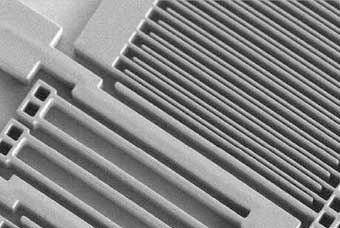

A: Large driver transistors with hundreds of fingers, even up to 1A current usage.

Q: How long do the simulation runs take?

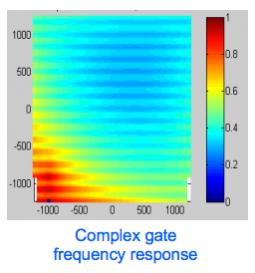

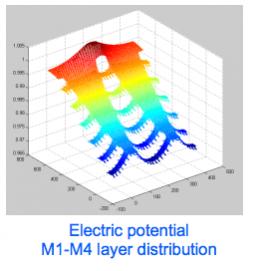

A: A large 1A device can be analyzed in just a few hours of time. The IR drop results are shown as a color map across all layers (metal, diffusion, 3D view of currents). This tool can be used stand-alone without a SPICE simulator.

Q: If you could change any feature of R3D what would it be, and why?

A: The features in R3D are quite good for analysis, we would like to change the rule setup to support more extraction commands of Calibre SVRF, more than a subset – we want a richer set supported.

Q: How is support at SFT?

A: Very good support provided by phone and email across the time zones (Germany to CA). We can ask for help in the afternoon by email and the next morning we have our answer.

Q: How often do you get updates from SFT?

A: We receive Quarterly updates, and so far there’s been no need for bug fixes.

Summary

In the analog mixed-signal design world X-FAB uses and recommends a 3D resistance extraction and analysis methodology in order to optimize driver designs. The R3D tool from Silicon Frontline Technology has been selected because of it’s accuracy and the 0.18 micrometer process called XH018 has a PDK developed.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center