Debugging an IC is never much fun because of all the file formats used, the levels of hierarchy and just the sheer design size, so when an EDA tool comes around that allows me to get my debugging done quicker, then I take notice and give it a look. I was already familiar with debugging SPICE netlists using a tool called SPICEVision Pro,… Read More

Tag: webinar

Webinar: OCV and Timing Closure Sign-off by Silvaco on Oct 10 at 10AM

The old adage that goes the one constant thing you can always count on is change, could easily be reworded for semiconductor design to say the one constant thing you can count on is variation. This is doubly true. Not only is variation, in all its forms, a constant factor in design, additionally the methods of analyzing and dealing … Read More

WEBINAR: AI-Powered Automated Timing Arc Prediction for AMS IP’s

A directed approach to reduce Risk and improve Quality

Safety and reliability are critical for most applications of integrated circuits (ICs) today. Even more so when they serve markets like ADAS, autonomous driving, healthcare and aeronautics where they are paramount. Safety and reliability transcend all levels of an integrated… Read More

WEBNAR: How ASIC/SoC Rapid Prototyping Solutions Can Help You!

If you are considering an FPGA prototype for an ASIC or SoC as part of your verification strategy, which more and more chip designers today are doing to enhance verification coverage of complex designs, please take advantage of this webinar replay:

How ASIC/SoC Prototyping Solutions Can Help You!

Or to get a quick quote from S2C … Read More

Adding CDM Protection to a Real World LNA Test Case

In RF designs Low Noise Amplifiers (LNA) play a critical role in system operation. They simultaneously need to be extremely sensitive and noise free, yet also must be able to withstand strong signal input without distortion. LNA designers often struggle to meet device performance specifications. Their task is further complicated… Read More

WEBINAR: Eliminating Hybrid Verification Barriers Through Test Suite Synthesis

I’ve been following the evolution of the verification space for a very long time including several stints consulting to formal verification companies. It has always been interesting to me to see how so many diverse verification techniques emerge and been used, but without much unification of the approaches. With the emergence… Read More

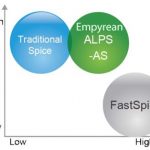

WEBINAR: GPU-Powered SPICE – The Way Forward for Analog Simulation

Several years ago, I was a consultant to a company called Gauda, Inc. I enjoyed working with Gauda as the technology was interesting. On June 3, 2014, Gauda, Inc. was acquired by D2S, Inc. so their technology lives on. Gauda was focused on optical proximity correction (OPC) and optical proximity verification solutions utilizing… Read More

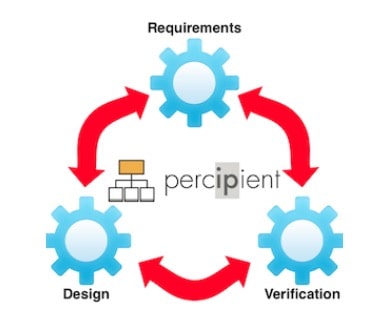

Webinar: ISO 26262 Compliance

To me the major idea of ISO 26262 compliance is ensuring that requirements can be traced throughout the entire design and verification process, including the use of IP blocks. The first market application that comes to mind with ISO 26262 is automotive, with its emphasis on safety because human lives are at stake. Since necessity… Read More

How to Spice Up Your Library Characterization

It used to be that at the mention of libraries, people would think of foundry PDK deliverables. However, now a host of factors such as automotive thermal requirements, nanometer FinFET processes, near threshold voltages, higher clock rates, high volumes, etc., have dramatically changed library development. These factors … Read More

Data Centers and AI Chips Benefit from Embedded In-Chip Monitoring

Webinars are a quick way to come up to speed with emerging trends in our semiconductor world, so I just finished watching an interesting one from Moortec about the benefits of embedded in-chip monitoring for Data Center and AIchip design. My first exposure to a data center was back in the 1960s during an elementary school class where… Read More