You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

There should be a link between iPhone H/W architecture and the incredible success of the product? Let’s assume and claim that this architecture, based on the internally developed ARM based A9 application processor, is simply the best on the market today…

Apple has implemented SSD in MacBook based on NVM Express (NVMe) protocol.… Read More

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More

The set of MIPI specifications has severely enlarged during the past year. This is a positive point, as the large set of specifications induces a wider choice, and a chip maker can decide to implement a complex specification to differentiate with competitors, or select a specification just tailored to support a basic architecture… Read More

At the beginning of December in Paris I had the opportunity to make a presentation to a very impressive audience, technical gurus from companies contributing to MIPI Alliance specification were here, including ST-Microelectronics, Intel, Qualcomm, TI, Toshiba, Nokia, Samsung, to name a few. … Read More

We have posted several blogs related to Cadence IP strategy, or I should say new strategy. Each of these blogs was dealing with a particular product, like PCI Express gen-3 Controller IP, latest DDR4 Memory Controller or Wide I/O. This approach was equivalent to describe trees, one after one, and finally ignoring the forest! It’s… Read More

As we know mobile industry is one of the fastest growing in the electronics arena, and it has led to the emergence of several standards of interfaces between processors, devices, storage, camera, keyboard and so on. The interfaces can involve hardware as well as software and can be complex. The standards are still evolving, often… Read More

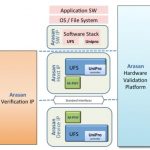

Storage interfaces for mobile are evolving rapidly, in particular with the Universal Flash Storage (UFS) standard. So how do you test a design? If you want to test a design that accesses, say, an SD card then you can wander into Fry’s and buy an SD card for a few dollars. But to design an interface to UFS is a bit harder since the … Read More

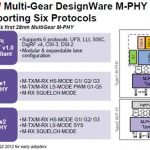

MIPI set of specifications (supported by dedicated controllers) are completed by a PHY function, the D-PHY or the M-PHY function. The D-PHY was the first to be released, and most of the MIPI functions supported in a smartphone we are using today probably still use a D-PHY, but the latest MIPI specifications have been developed based… Read More

There has been a general trend for over a decade now towards the use of very fast serial interfaces instead of wide parallel interfaces. This has been driven by a number of different factors ranging from the lack of pins on an SoC, the difficulty of keeping wide parallel interfaces free of skew, limitations on printed circuit board… Read More

The explosive growth in portable devices over the past decade has left manufactures in a quandary over how to add memory to their products that meet several criteria:

- High capacity

- Low cost

- Low power

- High bandwidth

…

Read More