Join us for our 6th Annual Virtual Prototyping Day and learn how you can “shift left” your development cycle with virtual prototypes.

Highly complex SoC and muti-die designs are putting pressure on silicon and software development teams to meet time-to-market demands. Virtual prototypes are the answer to begin… Read More

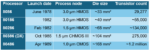

Hardware emulation arose as a necessity out of the needs of the eighties. By the mid-1980s, semiconductor designs had outgrown the practical limits of gate-level simulation. Gate-level simulation delivered accuracy, but at glacial pace; silicon prototypes performed at real-speed but arrived far too late. The industry needed… Read More

A recent announcement from Synopsys signals a meaningful escalation in the race to build next-generation AI hardware. The expanded collaboration between Synopsys and TSMC brings together silicon-proven IP, AI-driven design tools, and cutting-edge manufacturing processes in a tightly integrated effort to accelerate high-performance… Read More

In this webinar, Intel will present how EMIB-T (Embedded Multi-die Interconnect Bridge with TSVs) enables compact, cost-effective multi‑die design while sustaining the bandwidth and power efficiency required for AI and datacenter designs. Intel will share a production-oriented EMIB-T reference methodology built … Read More

As power integrity challenges increase with advanced nodes and multi-die architectures, EMIR analysis must evolve beyond traditional signoff. In this Synopsys webinar, we will show how RedHawk-SC is expanding its capabilities not only to enhance EMIR analysis, but also to enable IR-aware Static Timing Analysis (IR-STA) … Read More

This is a live panel with industry experts who are on the leading edge of AI in semiconductor manufacturing. This is a must attend event for all levels of semiconductor professionals. I hope to see you there.

The semiconductor industry faces unprecedented challenges as it pushes toward advanced nodes below 3nm, managing exponential… Read More

FPGA prototyping and hardware emulation originated from two independent demands that emerged at roughly the same time, namely, the necessity to implement digital designs in reconfigurable hardware. This was conceivable given the newly introduced field programmable gate array (FPGA) device.

Yet from the very beginning they… Read More

In this webinar, Marvell will present how its team accelerates passive interposer routing for advanced 2.5D/3.5D multi die designs by bringing early, physics based signal integrity feedback into each routing iteration. Rather than relying on repeated, compute intensive 3D FEM cycles during development, Marvell uses a Method… Read More