WIth packaging being one of the top sources of traffic on SemiWiki, I am expecting a big crowd at this event. A semiconductor substrate is a foundational material used in the fabrication of semiconductor devices. Substrates are a critical part of the manufacturing process and directly affect the performance, reliability, and… Read More

Tag: substrate

Maximizing ASIC Performance through Post-GDSII Backend Services

ASICs by definition are designed to meet the respective applications’ requirements. ASIC engineers deploy various design techniques to maximize performance, minimize power and reduce chip size. But is there more that can be done after the GDSII is taped out? A recent press release from Alchip Technology dated Feb 4, 2021 claims… Read More

Synopsys’ New Die-to-Die PHY IP – What It Means

This morning, Synopsys announced its new Die-to-Die PHY IP. This announcement is critically important as it addresses two major market drivers – the growing need for faster connectivity in the datacenter and similar markets, and a path to better exploit the latest processes by dealing with yield issues for larger dies in a different… Read More

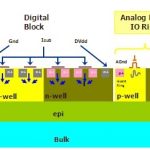

Analyze Substrate Noise in SoC Design?

Often substrate noise analysis takes place when everything is there on the chip, but that stage comes near the tape-out which is too late to make major changes in architecture, placement, introducing noise protection circuitry for the victims and so on. It was okay when there used to be very little analog content on the chip. But … Read More