I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

Tag: sram

TSMC ♥ Berkeley Design Automation

As I mentioned in BDA Takes on FinFET Based Memories with AFS Mega:

Is AFS Mega real? Of course it is, I’m an SRAM guy and I worked with BDA on this product so I know. But don’t take my word for it, stay tuned for endorsements from the top SRAM suppliers around the world.

Here is the first customer endorsement from the #1 foundry.… Read More

BDA Takes on FinFET-based Memories with AFS Mega

Berkeley Design Automation today announced the first silicon-accurate circuit simulation for mega-scale arrays like memories and CMOS image sensors. If this tool lives up to its claims, it is going to be a big deal for FinFET-based circuits, Memory designers are rightly worried about having the accuracy necessary to include… Read More

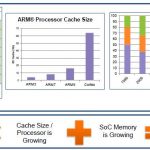

How much SRAM proportion could be integrated in SoC at 20 nm and below?

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More

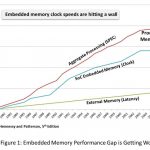

Current Embedded Memory Solutions Are Inadequate for 100G Ethernet

With an estimated 7 billion connected devices, the demand for rich content, including video, games, and mobile apps is skyrocketing. Service providers around the globe are scrambling to transform their networks to satisfy the overwhelming demand for content bandwidth. Over the next few years, they will be looking to network… Read More

The Business Case for Algorithmic Memories

Economic considerations are a primary driver in determining which technology solutions will be selected, and how they will be implemented in a company’s design environment. In the process of developing Memoir’s Algorithmic Memory technology and our Renaissance product line, we have held fast to two basic premises: Our technology… Read More

Mind the Gap — Overcoming the processor-memory performance gap to unlock SoC performance

Remember the processor-memory gap— a situation where the processor is forced to stall while waiting for a memory operation to complete? This was largely a result of the high latency required for off chip memory accesses. Haven’t we solved that problem now with SoCs? SoCs are typically architected with their processors … Read More

Synopsys STAR Webinar, embedded memory test and repair solutions

The acquisitions of Virage Logic by Synopsys in 2010, have allowed building a stronger, diversified IP port-folio, including the embedded SRAM, embedded non-volatile memory and embedded test and repair solution. Looking back in time, I remember the end of the 80’s: at that time the up-to-date solution to embed SRAM in your ASIC… Read More

40nm to 28nm Migration Success Story

The problem:To move dual-port SRAM library and macros from a 40nm process to a 28nm process. In addition to all the changes between two different foundry processes, the 28nm rules are disruptive and incompatible with the previous rules. The memory corecells (foundry-specific) would also need to be completely replaced.

Current… Read More

Thanks for the memory

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More