You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The current Coronavirus crisis is inflicting a lot of pain on people, companies, and governments. I hope I am not getting in trouble with my reasoning, but if you look closely, there are also some “positives” to the Covid-19 crisis.

– It is stress-testing our infrastructure and telling us where we need to improve – as country,… Read More

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

This conference will begin with a keynote address by my good friend Jim Hogan, EDA industry pioneer and venture capitalist. Jim has worked in the semiconductor design and manufacturing industry for more than 35 years and is very candid about his experience and vision for the future of EDA. This keynote and Q&A alone is worth … Read More

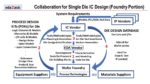

Standards have been proven to reduce cost of operations, drive greater process efficiencies and offer greater opportunities for start-up companies to infuse fresh technology in the design and manufacturing of IC’s. Si2 standards have been targeted to resolve “pinch-points” in the overall semiconductor supply chain… Read More

As I have been watching the developments in EDA and Semiconductor industry, it is apparent that we remain fragmented unless pushed to adopt a common standard mostly due to business reasons. Foundries are dictating on the rules to be followed by designs, thereby EDA tools incorporating them. Also, design companies needed to work… Read More

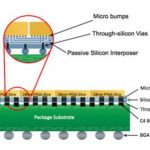

When process nodes reached 28 nm and below, it appeared that design density is reaching a saturation point, hitting the limits of Moore’s law. I was of the opinion that the future of microelectronic physical design was limited to 20 and 14 nm being addressed by technological advances such as FinFETs, double patterning, HKMG (High-k… Read More

3D Standardsby Paul McLellan on 02-01-2012 at 5:06 pmCategories: Ansys, Inc., EDA

At DesignCon this week there was a panel on 3D standards organized by Si2. I also talked to Aveek Sarkar of Apache (a subsidiary of Ansys) who is one of the founding member companies of the Si2 Open3D Technical Advisory Board (TAB), along with Atrenta, Cadence, Fraunhofer Institute, Global Foundries, Intel, Invarian, Mentor, Qualcomm,… Read More

In case you have not heard, the 16th Si2-hosted conference highlighting industry progress in design flow interoperability comes to Silicon Valley (Santa Clara, CA) on October 20th. Si2Con will showcase recent progress of members in the critical areas of:

[LIST=1]

Design tool flow integration (OpenAccess)

DRC / DFM / Parasitics…

Read More

OpenAccessby Paul McLellan on 06-21-2011 at 1:11 pmCategories: EDA

Probably everyone knows that openAccess is a layout database. It was originally developed at Cadence (called Genesis) but has since been transferred to Si2. Strictly speaking, openAccess is actually an API and the database is a reference implementation. The code is licensed under a sort of halfway to open-source: you can use … Read More

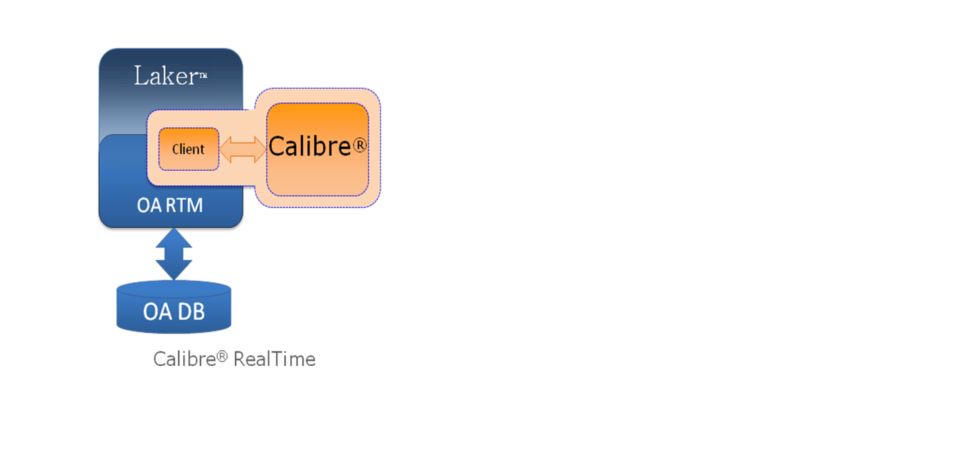

One of the first things that needs to be created when bringing up a new process is the Process Design Kit, or PDK. Years ago, back when I was running the custom IC business line at Cadence, we had a dominant position with the Virtuoso layout editor and so creating a PDK really meant creating a Virtuoso PDK, and it was a fairly straightforward… Read More