Babak A. Taheri, Ph.D., has served as Chief Executive Officer and member of the Silvaco board of directors from August 2019 to September 2021 and from November 2021 to present. From October 2018 to August 2019, Dr. Taheri served as our Chief Technology Officer and Executive Vice President of Products.

Tag: reram

2024 Outlook with Srinivasa Kakumanu of MosChip

MosChip is a publicly traded company founded in the year 1999, they offer semiconductor design services, turnkey ASIC, software services, and end-to-end product engineering solutions. The company headquartered in Hyderabad, India, with five design centers and over 1300 engineers located in Silicon Valley (USA), Hyderabad,… Read More

Weebit Nano Brings ReRAM Benefits to the Automotive Market

Non-volatile memory (NVM) is a critical building block for most electronic systems. The most popular NVM technology has traditionally been flash. As a discrete part, the technology can be delivered in various form factors. For embedded applications flash presents scaling challenges, however. A new NVM technology developed… Read More

2024 Outlook with Coby Hanoch of Weebit Nano

Weebit Nano is an Israeli semiconductor company that specializes in the development and commercialization of silicon oxide-based ReRAM (Resistive Random Access Memory) technology. ReRAM is a type of non-volatile memory that holds great promise for future computing and storage applications due to its potential for high density,… Read More

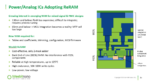

ReRAM Integration in BCD Process Revolutionizes Power Management Semiconductor Design

Weebit Nano, a leading developer of advanced memory technologies, recently announced a significant collaboration with DB HiTek, one of the top ten foundries of the world. The collaboration is designed to enable integration of Weebit’s Resistive Random-Access Memory (ReRAM) into DB HiTek’s 130nm Bipolar-CMOS-DMOS… Read More

A preview of Weebit Nano at DAC – with commentary from ChatGPT

Weebit Nano, a provider of advanced non-volatile memory (NVM) IP, will be exhibiting at the Design Automation Conference (DAC) this month. As part of this briefing I shared some of the basic the details with ChatGPT to see how it would phrase things. Here is some of what it suggested: “You won’t want to miss out on the epic experience… Read More

Podcast EP164: How Weebit Nano is Disrupting the Memory Market with Coby Hanoch

Dan is joined by Coby Hanoch, Coby joined Weebit Nano as CEO in 2017. He has 15 years of experience in engineering and engineering management roles, and 28 years of experience in sales management and executive roles.

Coby explains the unique features of Weebit Nano’s non-volatile ReRAM technology. He explores the technology’s… Read More

How an Embedded Non-Volatile Memory Can Be a Differentiator

Embedded memory makes computing applications run faster. In the early days of the semiconductor industry, the desire to utilize large amount of on-chip memory was limited by cost, manufacturing difficulties and technology mismatches between logic and memory circuit implementations. Since then, advancements in semiconductor… Read More

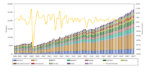

3rd Party Semiconductor Intellectual Property Market Update

The 3rd Party Semiconductor Intellectual Property (IP) market has seen great innovation in the products it offers to System-on-a-Chip (SoC) designers over the last ten years. If any market segment in the semiconductor industry typifies the intense evolutionary pressures that the entire electronics market has undergone, … Read More

Upcoming Webinar on Resistive RAM (ReRAM) Technology

On-chip memory (embedded memory) makes computing applications run faster. In the early days of the semiconductor industry, the desire to utilize large amount of on-chip memory was limited by cost, manufacturing difficulties and technology mismatches between logic and memory circuit implementations. Since then, advancements… Read More