My IC design career started out with manually sizing transistors to improve performance, while minimizing layout area and power consumption. Fortunately we don’t have to do manual transistor sizing anymore, thanks to EDA tools that are quicker and more accurate than manual methods. MunEDA is an EDA vendor that has developed… Read More

Tag: pvt corners

Fast and Accurate Variation-Aware Mixed-Signal Verification of Time-Domain 2-Step ADC

There is an interesting white paper out from Mentor on how a customer used the Solido Varation Designer tool to reduce Monte Carlo simulations. As you may know I worked for Solido for 10+ years up until they were acquired by Mentor in December of 2017. It was an incredible personal and professional experience. I have the highest respect… Read More

Achieving Design Robustness in Signoff for Advanced Node Digital Designs

I had the opportunity to preview an upcoming webinar on SemiWiki that deals with design robustness for signoff regarding advanced node digital designs (think single-digit nanometers). “Design robustness” is a key term – it refers to high quality, high yielding SoCs that come up quickly and reliably in the target system. We all… Read More

Low Power Design – Art vs. Science

I have heard many times before that low power and mixed-signal design is more Art than Science. I believe this is a misconception. Science is a field that builds upon previous experiences and discoveries. Art primarily seeks out creative differences, things we have not seen before that evoke emotion. The most successful designers… Read More

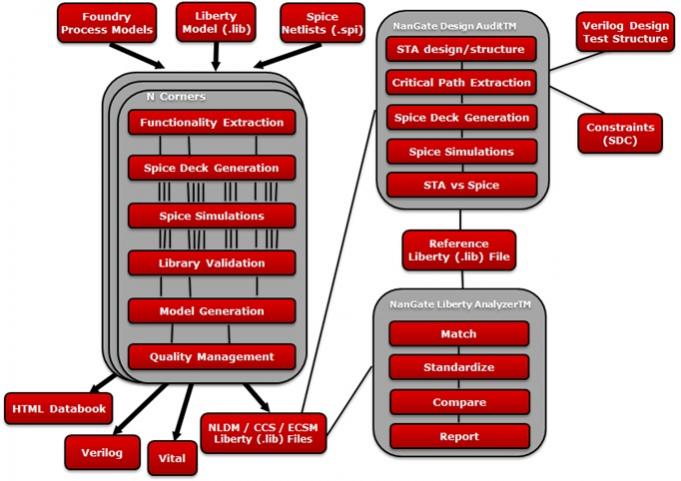

Silvaco WEBINAR: Nanometer Library Characterization Challenges and Solutions

As you may know, Silvaco has done some very clever acquisitions to fuel their unprecedented growth over the last five years. We have a wiki that tracks EDA Mergers and Acquisitions, Silvaco included, and it is the most viewed wiki on SemiWiki.com with 102,005 views thus far.

Silvaco acquired Nangate in March of 2018. NanGate got … Read More

Machine Learning Accelerates Library Characterization by 50 Percent!

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

Is Number of Signoff Corners an Issue?

Semiconductor companies continue to use the traditional corner-based signoff approach that has been developed more than 40+ years ago and has since remained mainly unchanged as an industry paradigm. Initially it had 2 corners, namely Worst Case (WC) and Best Case (BC) with the maximum and minimum cell delay respectively. Note… Read More

NanGate Launches Aggressive DAC Campaign: 50 Library Characterization Licenses for USD 50K

NanGate today announced a very aggressive “50-50 campaign”. Throughout June and July and in celebration of DAC 50th anniversary, NanGate will be offering 50 licenses of its Library Characterizer™ product for USD 50K for the first year. The offer applies to new customers as well as to existing customers that do not yet license the… Read More