When we get the notion of expansion of a company, it always provides a positive picture about something good happening to boost that expansion. There can be several reasons for expansion such as merger & acquisition, formation of joint venture or partnership, large customer orders and so on. However, organic expansion which… Read More

Tag: powerpro

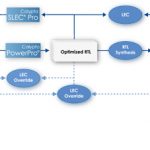

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

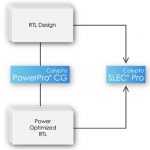

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

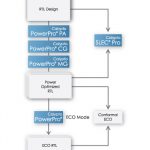

Addressing Power at Architectural and RTL Levels

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

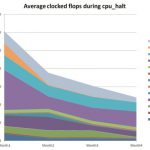

AMD Reduces Power by 20%

Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More

Clock Gating: Sequential Is Better

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

RTL Clock Gating Analysis Cuts Power by 20% in AMD Chip!

Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the… Read More

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More