Machine learning (ML) is already making its way into EDA tools and flows, but the majority of announcements have been around implementation, especially in guiding toward improved timing and area. This is a pretty obvious place to start; ML is in one sense an optimization technique, trained on prior examples, which should be able… Read More

Tag: pete hardee

Formal: Going Deep and Going Early

This year I got a chance to talk with Cadence at DVCon on a whole bunch of topics, so expect a steady stream of blogs over the next couple of months. First up was an update from Pete Hardee (Director of Product Management) on, surprise, surprise, formal verification. I’m always trying to learn more about this space, so I picked a couple… Read More

Getting to IP Functional Signoff

In the early days of IP reuse and platform-based design there was a widely-shared vision of in-house IP development teams churning out libraries of reusable IP, which could then be leveraged in many different SoC applications. This vision was enthusiastically pursued for a while; this is what drove reusability standards and … Read More

Formally Crossing the Chasm

Formal verification for hardware was stuck for a long time with a reputation of being interesting but difficult to use and consequently limited to niche applications. Jasper worked hard to change this, particularly with their apps for JasperGold and I have been seeing more anecdotal information that mainstream adoption is growing.… Read More

Next Generation Formal Technology to Boost Verification

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

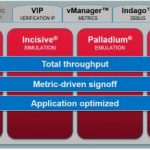

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More