Metal fill requirements for inductors are now a fact of life. Fill has long been seen as detrimental to device performance due to parasitic capacitance. The necessity of fill arises from the need to ensure planarization of dielectric layers by using chemical mechanical polishing. Without adequate fill, areas of the chip can suffer… Read More

Tag: peakview

Effect of Inductance on Interconnect

In previous design generations interconnect could safely be modeled by extraction using just R and C values. Parasitics in interconnect are important because they can affect the operating frequency or phase error in circuits like VCO’s. The need to model parasitics properly in wires is just as applicable in PA’s, LNA’s and for… Read More

Tackling Circuit Level EM Analysis for RF, MMW and High Speed Analog Designs

Accuracy, ease of use and performance have always been paramount for electromagnetic analysis software. Historically, it has been hard to find all three of these qualities in one tool. The result is that many high speed analog and RF designers resort to using multiple, often overlapping, tools to get the job done.

Lorentz Solution… Read More

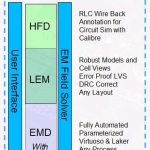

TSMC Threater Presentation: Lorentz Solution!

Lorentz Solution presented at TSMC’s DAC 2012 Open Innovation Platform Theater. The presenter was Lorentz Sales Director, Tom Simon. He presented what Lorentz calls its Electromagnetic Design and Analysis Platform. One of the main points of the talk was the cooperative work that Lorentz does with TSMC.