Terms like avalanche breakdown and impact ionization sound like they come from the world of science fiction. They do indeed come from a high stakes world, but one that plays out over and over again here and now, on a microscopic scale in semiconductor devices – namely as part of electrostatic discharge (ESD) protection. Semiconductor… Read More

Tag: parasitic bjt

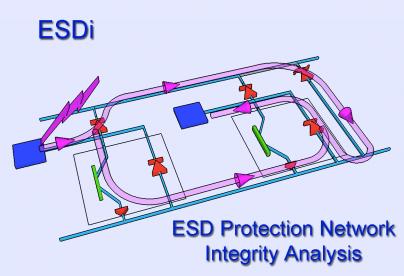

ESD Protection Network Checking is Difficult But Necessary

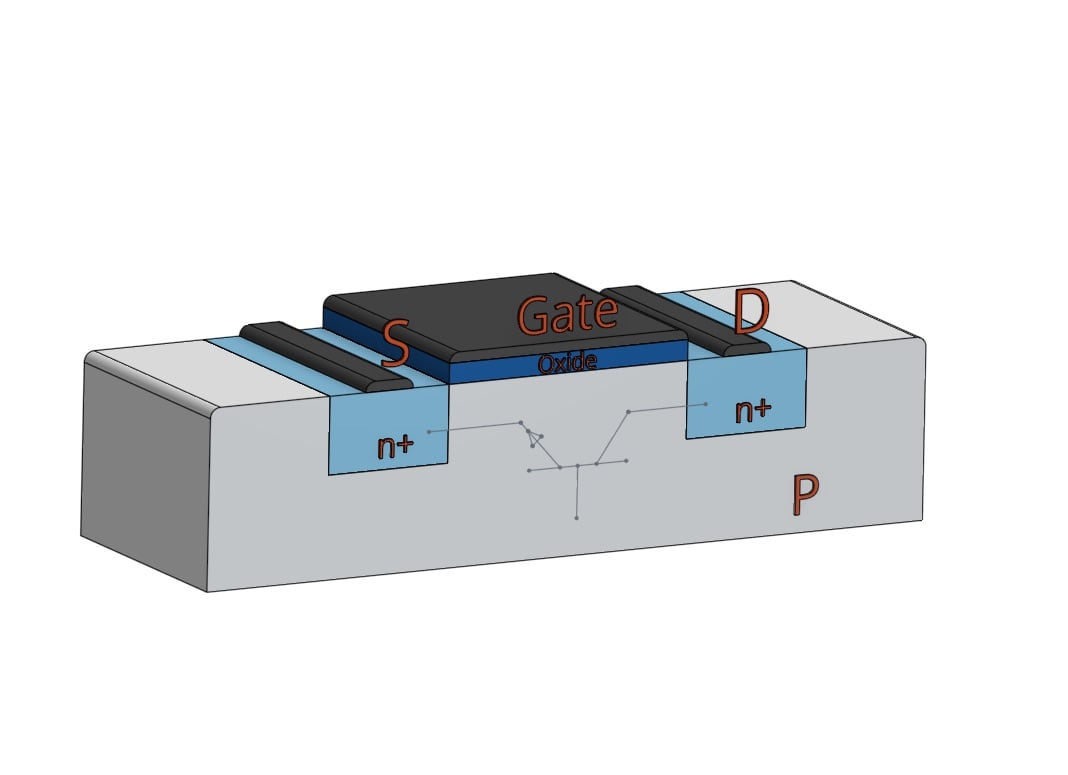

I’ve written before about anti-fuse non-volatile memory, where the gate oxide is intentionally damaged in order to create a readable bit of data, but this is what most circuit designers never want to have happen to their logic gates. However, since the advent of MOS transistors the issue of Electrostatic Discharge (ESD) and the… Read More