Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Tag: pace

ST Endorses PowerArtist with ARM Cores & FDSOI libs

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

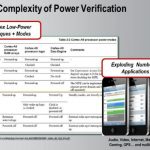

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Apache Power Artist Capabilities I

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More