The explosive growth of AI and accelerated computing is placing unprecedented demands on system-on-chip (SoC) design. Modern AI workloads require extremely high bandwidth, ultra-low latency, and energy-efficient data movement across increasingly heterogeneous architectures. As SoCs scale to incorporate clusters of… Read More

Tag: npu

Ceva Unleashes Wi-Fi 7 Pulse: Awakening Instant AI Brains in IoT and Physical Robots

In the rapidly evolving landscape of connected devices, where artificial intelligence meets the physical world, Ceva has unveiled a groundbreaking solution: the Ceva-Waves Wi-Fi 7 1×1 client IP. Announced on October 21, 2025, this IP core is designed to supercharge AI-enabled IoT devices and pioneering physical AI systems,… Read More

A Novel Approach to Future Proofing AI Hardware

There is a built-in challenge for edge AI intended for long time-in-service markets. Automotive applications are the obvious example, while aerospace and perhaps medical usage may impose similar demands. Support for the advanced AI methods we now expect – transformers, physical and agentic AI – is not feasible without dedicated… Read More

From All-in-One IP to Cervell™: How Semidynamics Reimagined AI Compute with RISC-V

In an era where artificial intelligence workloads are growing in scale, complexity, and diversity, chipmakers are facing increasing pressure to deliver solutions that are not only fast, but also flexible and programmable. Semidynamics recently announced Cervell™, a fully programmable Neural Processing Unit (NPU) designed… Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V Solution

Founded with a vision to create transformative, customizable IP solutions, Semidynamics has emerged as a significant player in the AI hardware industry. Initially operating as a design engineering company, Semidynamics spent its early years exploring various pathways before pivoting to develop proprietary intellectual… Read More

The Fallacy of Operator Fallback and the Future of Machine Learning Accelerators

As artificial intelligence (AI) and machine learning (ML) models continue to evolve at a breathtaking pace, the demands on hardware for inference and real-time processing grow increasingly complex. Traditional hardware architectures for acceleration are proving inadequate to keep up with these rapid advancements in ML … Read More

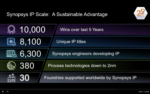

Synopsys Design IP for Modern SoCs and Multi-Die Systems

Semiconductor intellectual property (IP) plays a critical role in modern system-on-chip (SoC) designs. That’s not surprising given that modern SoCs are highly complex designs that leverage already proven building blocks such as processors, interfaces, foundational IP, on-chip bus fabrics, security IP, and others. This… Read More

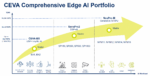

Navigating Edge AI Architectures: Power Efficiency, Performance, and Future-Proofing

The surge in Edge AI applications has propelled the need for architectures that balance performance, power efficiency, and flexibility. Architectural choices play a pivotal role in determining the success of AI processing at the edge, with trade-offs often necessary to meet the unique demands of diverse workloads. There are… Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More

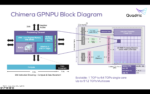

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More