The great thing about competition in free markets is that vendors are always pushing their products to find an edge. You the consumer don’t have to do much to take advantage of these advances (other than possibly paying for new options). You just sit back and watch the tool you use get faster and deliver better QoR. You may think that… Read More

Tag: multi-core

MIPS 64 bit CPU Architecture

Imagination Technologies has just launched the 5[SUP]th[/SUP] generation of MIPS CPU core, the 64-bits Warrior, or I6400 family, offering a total compatibility with the 32-bit previous architecture. MIPS Warrior I-class processor cores offers 64-bit processing in applications including embedded, mobile, digital consumer,… Read More

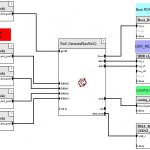

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More