When describing the complexity of deep sub-micron systems on chip (SoCs), most engineers and their managers tend to refer to a combination of gate count, amount of embedded memory, and frequency of operation. If one’s task is to assess the complexity of the physical design effort for a given SoC, then there are numerous additional… Read More

Tag: mosys

Such a small piece of Silicon, so strategic PHY IP

How could I talk about the various Interface protocols (PCIe, USB, MIPI, DDRn…) from an IP perspective and miss the PHY IP! Especially these days, where the PHY IP market has been seriously shaken, as we will see in this post, and will probably continue to be shaken… but we will have to wait and look at the M&A news during the next … Read More

EDA Tool Flow at MoSys Plus Design Data Management

I’ve read about MoSys over the years and had the chance this week to interview Nani Subraminian, Engineering Manager about the types of EDA tools that they use and how design data management has been deployed to keep the design process organized. My background includes both DRAM and SRAM design, so I’ve been curious… Read More

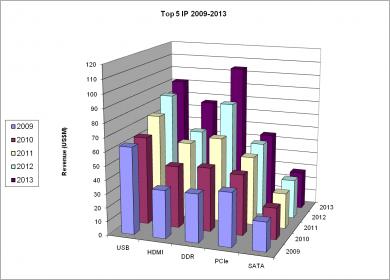

DDR4 Controller IP, Cadence IP strategy… and Synopsys

I will share with you some strategic information released by Cadence last week about their IP strategy, more specifically about the launch of the DDR4 Controller IP. And try to understand Cadence strategy about Interface IP in general (USB, PCIe, SATA, DDRn, HDMI, MIPI…) and how Cadence is positioned in respect with their closest… Read More