In the early days of RISC-V adoption, applications were microcontroller-centric with no need for virtualization support. But horizons expanded and now RISC-V is appearing in application processors, very much needing to be able to virtualize multiple apps concurrently. Take another step forward to datacenter servers running… Read More

Tag: mmu

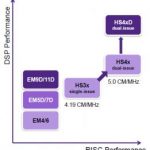

Is ARC HS4xD Family More a CPU or DSP IP Core?

When I had to define the various IP categories (processor, analog & mixed-signal, wired interfaces, etc.) to build the Design IP Report, I scratched my head for a while about the processor main category: how to define the sub-categories? Not that long ago, it was easy to identify a CPU IP core and a DSP IP core. As of today, if a DSP… Read More

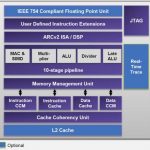

Linux and the ARC of the Coherent

Remember that thing called “real-time Linux”? Yeah, nobody else does either. As builds became configurable and clock speeds increased, embedded Linux manifested itself as fast enough for many applications – if a few other SoC details are addressed.

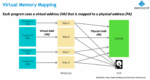

Most obvious for SoCs to run Linux is the need for a fully integrated MMU implementation.… Read More