It used to be that at the mention of libraries, people would think of foundry PDK deliverables. However, now a host of factors such as automotive thermal requirements, nanometer FinFET processes, near threshold voltages, higher clock rates, high volumes, etc., have dramatically changed library development. These factors … Read More

Tag: library

The Rebirth of Dolphin Integration!

You may have seen this Press Release (see below) announcing that Dolphin Integration (Dolphin) has been acquired by Soitec (60%) and MBDA (40%) – you can see more information about these two companies at the bottom of this blog. Founded in 1985, Dolphin had some recurrent cash flow issues during the last couple of years, that they… Read More

When it Comes to Process Migration, “Standard Cells” are Anything But

Standard cell library developers are faced with a daunting task when it is time to create a library for a new process node. Porting an existing library can be a big help, but even then, manual modifications to 800 or more cells is still required. Each of those cells has many geometric elements are that affected by new design rules. All… Read More

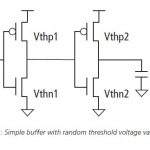

Solutions for Variation Analysis at 16nm and Beyond

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

How Good Is Your Library? Are You Sure?

One task that is not very exciting but is critical is that of library quality assurance. Many design groups have created their own procedures, often having been burned in the past, to ensure that the libraries that they use are good. Failure to do so has resulted in:… Read More

Shorten the Learning Curve for High Level Synthesis

When chip designers moved from a gate-level design methodology to coding with RTL there was a learning curve involved, and the same thing happens when you move from RTL to High Level Synthesis (HLS) using C++ or SystemC coding. One great shortcut to this learning curve is the use of pre-defined library functions. I just heard about… Read More

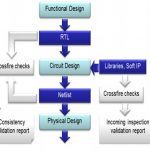

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More