For advanced semiconductor designs, achieving both design rule check clean layouts and optimal electrical performance is crucial for minimizing design iterations, reducing time-to-market and ensuring product reliability. Balancing electrical performance and layout integrity is a difficult task. Achieving an optimal… Read More

Tag: jeff wilson

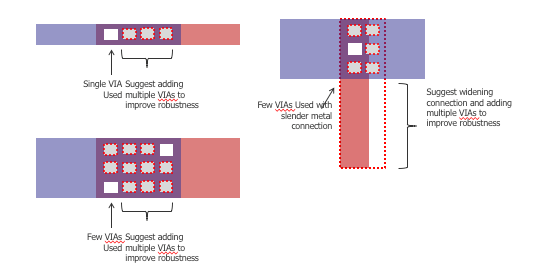

Calibre DesignEnhancer Improves Power Management Faster and Earlier

Anyone who has attempted to implement a custom design in an advanced process node knows that effective power management can be quite challenging. Effects such as voltage (IR) drop and electromigration (EM) can present significant headaches for both design teams and foundries. Optimizing layouts for these kinds of issues is … Read More

Foundry Partnership Simplifies Design for Reliability

This builds on a couple of topics I have covered for quite a while from an analysis point of view – integrity and reliability. The power distribution network and some other networks like clock trees are particularly susceptible to both IR-drop and electromigration (EM) problems. The first can lead to intermittent timing failures,… Read More