Back in the 2008 financial Crises, GM was finally brought to its knees and had to face a radical makeover. They asked for a bailout from the government that allowed the unions to swap out lower compensation for equity, something no union would do unless the alternative was to shutter the doors. The bondholders and the shareholders… Read More

Tag: ibm

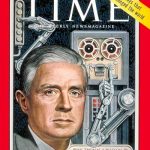

From IBM Mainframes to Wintel PCs to Apple iPhones: 70% is the Magic Number

Time to ring the Bell. With the iPhone 4S, Apple has just surpassed the 70% gross margin metric that usually equates to a compute platform becoming an industry standard. IBM’s mainframe achieved it in the 1960s with the 360 series and still is able to crank it out with their Z-series. The combined Intel and Microsoft tandem (Wintel)… Read More

HP Will Farm Out Server Business to Intel

In a Washington Post Column this past Sunday, Barry Ritholtz, A Wall St. Money Manager and who has a blog called the Big Picture, recounts the destruction that Apple has inflicted on a wide swath of technology companies (see And then there were none). He calls it “creative destruction writ large.” Ritholtz though is only accounting… Read More

TSMC Versus The FabClub!

The Common Platform Technology Forum last week was not well attended, less than half than the GlobalFoundries Conference. It was deja vu of previous CP forums but there were a couple of surprises to go with the disappointment. The lunch line was long, but fortunately I was escorted to the press lunch featuring VIP’s from Samsung,… Read More

Getting to the 32nm/28nm Common Platform node with Mentor IC Tools

Last week I talked with two experts at Mentor about the challenges of getting IC designs into the 32nm/28nm node on the Common Platform (IBM, GLOBALFOUNDRIES and Samsung). Global Foundries issued a press release talking about how the four major EDA companies have worked together to qualify EDA tools for this node.

Sudhakar Jilla,… Read More

Critical Area Analysis and Memory Redundancy

Simon Favre, one of our Calibre Technical Marketing Engineers, presented a paper on Critical Area Analysis and Memory Redundancy at the 2010 IEEE North Atlantic Test Workshop in Hopewell Junction, NY, just up the road from Fishkill. As Simon says…

Fishkill, New York. IBM is in Fishkill. IBM invented Critical Area Analysis in what,… Read More