MosChip is a publicly traded company founded in the year 1999, they offer semiconductor design services, turnkey ASIC, software services, and end-to-end product engineering solutions. The company headquartered in Hyderabad, India, with five design centers and over 1300 engineers located in Silicon Valley (USA), Hyderabad,… Read More

Tag: hmc

Emergence of Segment-Specific DDRn Memory Controller

The semiconductor industry is served today by memory devices supporting various protocols, like DDR4, DDR3, LPDDR4, LPDDR3, GDDR5, HBM, HMC, etc. The trend is clearly to define application specific memory-protocols and in some cases, application specific devices. But developing many, and different, memory controllers … Read More

Which High B/W Memory to Select after DDR4?

Once upon a time, RAM technology was the driver of the semiconductor process. DRAM products were the first to be designed on a newest technology node and DRAM was used as a process driver. It was 30 years ago and the most aggressive process nodes were ranging between 1um and 1.5 um (1 500 nm!). Then in the 1990 the Synchronous Dynamic … Read More

Cadence white paper helps you selecting what come after DDR4

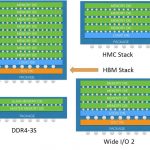

The DRAM market is shaking… In 2014, analysts predict that LPDDR4 will surpass DDR4 for the first time. When releasing DDR4 standard, JEDEC has clearly stated that the industry should not expect any DDR5. Does this means that DRAM technology new development is ending with DDR4? According with Mike Howard, principal analyst at … Read More

Hybrid Memory Cube and the Intel Knights Landing

While looking for information on a Xilinx Spartan 6 Project with DDR memory I came across a new type of DRAM called the Hybrid Memory Cube (HMC). The technology made me want to take a closer look:

The Hybrid Memory Cube is like a stack of DDR chips stacked die on die using through silicon vias to interconnect the dies the bottom die in not… Read More

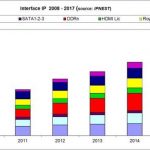

What’s new in the “Interface IP Survey” ?

The reader will find many updates in the “Interface IP Survey” from IPNEST, released in October 2013. Good question, as the IP market is a very fast moving one and the protocol based Interface IP, is moving even faster… exhibiting 20% growth rate in 2012, expected to grow with 10% CAGR between 2012 and 2017 to reach $700M. … Read More

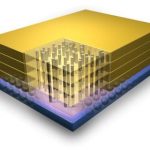

Hybrid Memory Cube Shipping

Today Micron announced that it is shipping 2GB Hybrid Memory Cube (HMC) samples. The HMC is actually 5 stacked die connected with through-silicon-vias (TSVs). The bottom die is a logic chip and is actually manufactured for Micron in an IBM 32nm process (and doesn’t have any TSVs). The other 4 die are 4Gb DRAM die manufactured… Read More

Emerging Trend – Choose DRAM as per Your Design Need

Lately I was studying about new innovations in memory world such as ReRAM and Memristor. As DRAM (although it has become a commodity) has found its extensive use in mobile, PC, tablet and so on, that was an inclination too to know more about. While reviewing Cadence’s offering in memory subsystems, I came across this whitepaperwhich… Read More

Did you miss Cadence’s MemCon?

That’s too bad, as you have missed latest news about the Hybrid Memory Cube (presentation by Micron), Wide I/O 2 standard, as well as other standards like LPDDR4, eMMC 5.0, and LRDIMM,the good news is that you may find all these presentations on MemCon proceedings web site.

I first had a look at Richard Goering excellent blog: wideI/O… Read More

3D Memories

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More