As analog and mixed-signal designs become increasingly complex, parasitic effects dominate both design time and cost, consuming 30–50% of engineers’ effort in debugging and reanalyzing circuits. Addressing these multiphysics effects requires early verification strategies and reliable simulation solutions. Modern … Read More

Tag: electrostatic discharge

3D ESD verification: Tackling new challenges in advanced IC design

By Dina Medhat

Three key takeaways

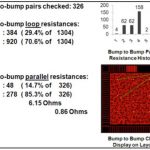

- 3D ICs require fundamentally new ESD verification strategies. Traditional 2D approaches cannot address the complexity and unique connections in stacked-die architectures.

- Classifying external and internal IOs is essential for robust and cost-efficient ESD protection. Proper differentiation

Protect against ESD by ensuring latch-up guard rings

By Mark Tawfik

Overview: Protecting ICs from costly ESD and latch-up failures

Electrostatic discharge (ESD) events cost the semiconductor industry an estimated $8 billion annually in lost productivity, warranty claims and product failures [1].

Ensuring the robust protection of integrated circuits (ICs) against various… Read More

Semitracks Course: EOS, ESD and How to Differentiate

Electrical Overstress (EOS) and Electrostatic Discharge (ESD) account for most of the field failures observed in the electronics industry. Although EOS and ESD damage can at times look quite similar to each other, the source each and the solution can be quite different. Therefore, it is important to be able to distinguish between… Read More

Stressed out about Electrostatic Discharge (ESD) or Electrical Overstress (EOS)?

Do not lose sleep worrying that your integrated circuits might fail during EOS/ESD events. Join us for the 38th annual EOS/ESD Symposium in Anaheim, CA in September. Experts on the field will address the latest research on EOS and ESD in the rapidly changing world of electronics.

As electronics continue to become commonplace in… Read More

Lake Tahoe: The Center of ESD Innovation

Almost anyone that is active in IC design will be “in touch” with Electrostatic Discharge (ESD) at some time (pun intended). Preventing ESD related IC failures remains something like black magic—at least it’s easy to get that feeling when you are trying to debug ESD failures. I/O and ESD layouts that resulted in excellent robustness… Read More

First Time, Every Time

While this iconic advertising phrase was first used to describe the ink reliability of a ballpoint pen, it perfectly summarizes the average consumer’s attitude toward automobile reliability as well. We don’t really care how it’s done, as long as everything in our car works first time, every time. Even when that includes heated… Read More

Automating Complex Circuit Checking Tasks

By Hend Wagieh, Mentor Graphics

At advanced IC technology nodes, circuit designers are now encountering problems such as reduced voltage supply headroom, increased wiring parasitic resistance (Rp) and capacitance (Cp), more restrictive electromigration (EM) rules, latch-up, and electrostatic discharge (ESD) damage,… Read More

Electro-static Discharge (ESD)

Electro-static discharge (ESD) has been a problem since the beginning of IC production. Chips function on power supplies of up to a few volts (depending on the era) whereas ESD voltages are measured in the thousands of volts. When you reach out for your car door handle and a spark jumps across, that is ESD. If you were touching a chip… Read More