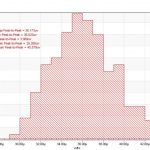

Tanner EDA Applications Engineers see a broad range of technical challenges that our users are trying to overcome. Here’s one worth sharing – it deals with transient noise analysis (TNA) for a comparator design. The customer is a producer of advanced flow measurement devices for application in medicine and research. The designer… Read More

Tag: eda

MOS-AK/GSA Munich Workshop

The MOS-AK/GSA Modeling Working Group, a global compact modeling standardization forum, completed its annual spring compact modeling workshop on April 11-12, 2013 at the Institute for Technical Electronics, TUM, Munich. The event received full sponsorship from leading industrial partners including MunEDA and Tanner EDA.… Read More

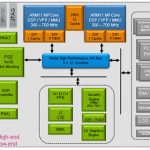

Challenges of 20nm IC Design

Designing at the 20nm node is harder than at 28nm, mostly because of the lithography and process variability challenges that in turn require changes to EDA tools and mask making. The attraction of 20nm design is realizing SoCs with 20 billion transistors. Saleem Haider from Synopsys spoke with me last week to review how Synopsys… Read More

Reduce Errors in Multi-threaded Designs

Many advanced algorithmic IPs are described in C++. We use this language because of its flexibility. Of course software algorithms are written to be executed on processors so they don’t solve all the issues of getting the algorithm implemented in hardware directly. This is not simply a high-level synthesis (HLS) issue. Usually… Read More

Using Virtual Platforms to Make IP Decisions

Most SoC designs these days consist largely, but not entirely, of purchased IP blocks. But there are lots of tradeoffs involved in selecting IP blocks, and since those tradeoffs change with process node, even decisions that seem “obvious” based on the last generation of the design, may not be so clear cut. Even if you… Read More

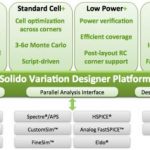

TSMC ♥ Solido

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse… Read More

Mentor CEO Wally Rhines U2U Keynote

You will never meet a more approachable CEO in the semiconductor ecosystem than Dr. Walden C. Rhines. The first time I met Wally was way back when I blogged for food and he invited me over for lunch. Even better, a year or two later I was having dinner with a friend at the DBL Tree in San Jose. Wally was waiting for his flight home so he joined… Read More

Best Practice for RTL Power Design for Mobile

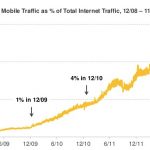

Mobile devices are taking over the world. If you want lots of graphs and data then look at Mary Meeker’s presentation that I blogged about earlier this week. The graph on the right is just one datapoint, showing that mobile access to the internet is probably up to about 15% now from a standing start 5 years ago.

Of course, one obvious… Read More

ESD – Key issue for IC reliability, how to prevent?

It’s a common electrical rule that when large amount of charge gets accumulated, it tries to break any of its surrounding isolation. Although it wouldn’t have been prominent in 1980s or 90s, protection for ICs from such damaging effects is a must, specifically in large mixed-signal designs of today, working at different voltages… Read More

Forte Rises

Over the past few months there has been a bit of back-and-forth concerning the 2012 market data indicating that Forte Designs Systems had taken over the top spot (by revenue) in the high-level synthesis (HLS) market (see stories hereand here). Having worked in this segment for Synfora as VP of Marketing, and as a consultant to AutoESL,… Read More