Since power has become a critical factor in semiconductor chip design, the stress is towards decreasing supply voltage to reduce power consumption. However, the threshold voltage to switch devices cannot go down beyond a certain limit and these results in an extremely narrow margin for noise between the two. And that gets further… Read More

Tag: decap

A Collaborative Approach Yields Better PI for PCBs

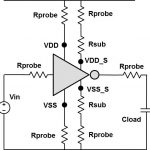

The power integrity (PI) of a system is an extremely important aspect to be looked at all levels – chip, package and PCB for overall reliability of the system. At the PCB level, a DC analysis, usually based on IR drop, must ensure that adequate DC voltage, satisfying all constraints of current density and temperature, is delivered… Read More

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More