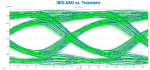

High-speed digital (HSD) designers have long tested the limits of realizable speed. GHz frequencies are now the norm, and multi-level signaling is pushing rates higher while the long-awaited transition to optical signaling and even higher rates looms ever closer. Power density is also climbing, and data-hungry applications… Read More

Tag: crosstalk

Keysight EDA 2025 launches AI-enhanced design workflows

The upcoming Keysight EDA 2025 launch has three familiar tracks: RF circuit design, high-speed digital circuit design, and device modeling and characterization. However, this update features a common thread between the tracks – AI-enhanced design workflows. AI speeds modeling and simulation, opening co-optimization for… Read More

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

Samtec Demystifies Signal Integrity for Everyone

As clock speeds go up, voltages go down and data volumes explode the need for fast, reliable and low latency data channels becomes critical in all kinds of applications. Balancing the requirements of low power and high performance requires the mastery of many skills. At the top of many lists is the need for superior signal integrity,… Read More

Samtec Lets You Learn from Home with a Great Webinar Lineup

Work from home (WFH) has become a normal occurrence this past year. “Do you work from home?” “Of course, where else?” Samtec is taking the whole work from home thing up a notch with a new webinar lineup for 2021. Back by popular demand, they are launching a new series of educational webinars. Started last year, the gEEk SpEEk Webinar… Read More

Designing Next Generation Memory Interfaces: Modeling, Analysis, and Tips

At DesignCon 2020, there was a presentation by Micron, Socionext and Cadence that discussed design challenges and strategies for using the new low-power DDR specification (LPDDR5). As is the case with many presentations at DesignCon, ecosystem collaboration was emphasized. Justin Butterfield (senior engineer at Micron)… Read More

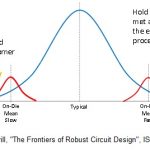

The Latest in Static Timing Analysis with Variation Modeling

In many ways, static timing analysis (STA) is more of an art than a science. Methodologists are faced with addressing complex phenomena that impact circuit delay — e.g., signal crosstalk, dynamic I*R supply voltage drop, temperature inversion, device aging effects, and especially (correlated and uncorrelated) process… Read More