You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

If the thought of a silicon respin keeps you awake at night, you’re not alone. Re-fabricating a chip can cost tens of millions of dollars. An unplanned respin also risks a delay in getting a product to market, which adds tremendous costs in terms of lost business.

Undoubtedly, adding to your sleep loss is the recent rise in respins.… Read More

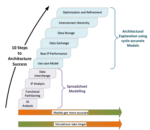

Sondrel just released a position paper on how to model and design a complex ASIC. We have been following Sondrel for the past year and I have found their collateral to be excellent. Here is the position paper overview, a description of the new Sondrel modeling tool, the 10 steps, and of course a link to download the paper:

Overview

It… Read More

The difficulty of managing the power domains on a complex SoC led to the development of a power format file description, to serve as the repository for data needed for functional and electrical analysis (e.g., CPF, UPF). Yet, what about complex printed circuit boards? How can the power domain information be effectively represented… Read More

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More