Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Tag: clock tree synthesis

Performance, Power and Area (PPA) Benefits Through Intelligent Clock Networks

One of the sessions at the Linley Fall Processor Conference 2021 was the SoC Design session. With a horizontal focus, it included presentations of interest to a variety of different market applications. The talk by Mo Faisal, CEO of Movellus, caught my attention as it promises to solve a chronic issue relating to synchronizing … Read More

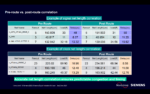

Synopsys Fusion Compiler Delivers ARM Hercules-Samsung 5LPE Design

There were many interesting presentations at ARM TechCon this year besides the keynote addresses by Arm, which were truly stunning for content and production value. One very interesting presentation was the talk given in the afternoon of Wednesday, October 9, 2019, titled, Synopsys Fusion Compiler for Next Generation Arm Hercules… Read More

How Good Are Your Clocks?

One of the trickiest tasks in designing a modern SoC is getting the clock tree(s) right. The two big reasons for this:

- the clocks can consume 30% or more of the power of the whole chip, so minimizing the number of buffers inserted is critical to keeping power under control

- the clock insertion delay and clock skew have a major impact on

Cadence aquires Azuro

Cadence this morning announced that it has acquired Azuro. Azuro has become a leader in building the clock trees for high performance SoCs. A good rule of thumb is that the clock consumes 30% of the power in an SoC so optimizing it is really important. Terms were not disclosed.

The clock trees involve clock gating which can reduce clock… Read More