The relentless advancement of mobile phone technology continues to push boundaries, demanding SoCs that deliver ever-increasing performance while preserving extensive battery life. To meet these demands, the industry is progressively embracing lower technology nodes with current designs being taped-out at 5nm or below.… Read More

Tag: clock

Clock Aging Issues at Sub-10nm Nodes

Semiconductor chips are all tested prior to shipment in order to weed out early failures, however there are some more subtle reliability effects that only appear in the longer term, like clock aging. There’s even a classic chart that shows the “bathtub curve” of failure rates over time:

If reality and expectations… Read More

Analyzing Clocks at 7nm and Smaller Nodes

In the good old days the clock signal looked like a square wave , and had a voltage swing of 5 volts, however with 7nm technology the clock signals can now look more like a sawtooth signal and may not actually reach the full Vdd value of 0.65V inside the core of a chip. I’ll cover some of the semiconductor market trends, and then challenges… Read More

Netlist CDC. Why You Need it and How You do it.

The most obvious question here is “why do I need netlist CDC?” A lot of what you’re looking for in CDC analysis is really complex behaviors, like handshakes between different clock domains, correct gray coding in synchronizing FIFOs, eliminating quasi-static signals and the like. Deeply functional, system-level intent stuff.… Read More

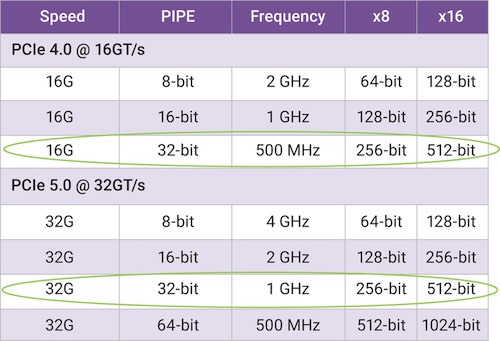

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

How Good Are Your Clocks?

One of the trickiest tasks in designing a modern SoC is getting the clock tree(s) right. The two big reasons for this:

- the clocks can consume 30% or more of the power of the whole chip, so minimizing the number of buffers inserted is critical to keeping power under control

- the clock insertion delay and clock skew have a major impact on

Properly Handing Of Clock Tree Synthesis Specifications

Given today’s design requirements with respect to low power, there is increasing focus on the contribution to total power made by a design’s clock trees. The design decisions made by the front-end team to achieve high performance without wasting power must be conveyed to back-end team. This hand-off must be accurate… Read More