Introduction

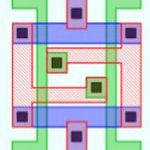

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

Tag: calibre

Who Needs a 3D Field Solver for IC Design?

Inroduction

In the early days we made paper plots of an IC layout then measured the width and length of interconnect segments with a ruler to add up all of the squares, then multiplied by the resistance per square. It was tedious, error prone and took way too much time, but we were rewarded with accurate parasitic values for our SPICE… Read More

DRC/DFM inside of Place and Route

Intro

Earlier this month I drove to Mentor Graphics in Wilsonville, Oregon and spoke with Michael Buehler-Garcia, Director of Marketing and Nancy Nguyen, TME, both part of the Calibre Design to Silicon Division. I’m a big fan of correct-by-construction thinking in EDA tools and what they had to say immediately caught my… Read More

Getting Real Time Calibre DRC Results

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout

New ERC Tools Catch Design Errors

A growing number of reports highlight a class of design errors that is difficult to check using more traditional methods, and can potentially affect a wide range of IC designs, especially where high reliability is a must.By Matthew Hogan

Today’s IC designs are complex. They contain vast arrays of features and functionality in … Read More

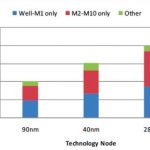

Computational Lithography, Scaling’s Best Friend

By Joseph Sawicki, Vice President & General Manager, Design to Silicon Division

It is one of the more amazing stories in the continued march of Moore’s Law over the past four nodes. Previously scaling was enabled solely though changes in the physical domain, whether through decreasing the wavelength of light, increasing … Read More