In forty plus years as a semiconductor professional I have never seen a semiconductor design ecosystem build as fast and as strong as RISC-V. As a result, RISC-V Now! has emerged as a pivotal gathering, a conference with a clear and ambitious mission: To transform the open, modular, and flexible RISC-V ISA from an exciting specification… Read More

Tag: cadence

Post-Silicon Validating an MMU. Innovation in Verification

Some post-silicon bugs are unavoidable, but we’re getting better at catching them before we ship. Here we look at a method based on a bare-metal exerciser to stress-test the MMU. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A)… Read More

2025 Retrospective. Innovation in Verification

As usual in January we start with a look back at the papers we reviewed last year. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas. As always, feedback welcome.

Looking back at 2025

… Read MoreCadenceLIVE Silicon Valley 2026

Join us on April 16 for CadenceLIVE Silicon Valley 2026, where Cadence technology users connect with the engineers and industry leaders who develop the solutions and the industry experts who influence market trends.

Participants experience a day of learning, connection, and cutting-edge technology shaping the future of electronic… Read More

Agentic Bug Localization. Innovation in Verification

Bug localization continues to be a challenge for both bug triage and root-cause analysis. Agentic approaches suggest a way forward. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas.… Read More

Cadence’s Strategic Leap: Acquiring Hexagon’s Design & Engineering Business

In a bold move that underscores the accelerating convergence of electronic design automation (EDA) and mechanical engineering, Cadence Design Systems announced its agreement to acquire Hexagon AB’s Design & Engineering (D&E) business for approximately €2.7 billion, equivalent to about $3.16 billion. This… Read More

Chiplet Summit 2026

All the Solutions for Developing Chiplets

2025 Keynote Addresses from Industry Leaders:

Alphawave Semi, Arm, Cadence Design Systems, Keysight, Open Compute Project, Synopsys, Teradyne

2025’s Main Topics Included:

AI/ML Acceleration, Open Chiplet Economy, Advanced Packaging Methods, Die-to-die Interfaces, Working … Read More

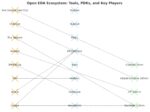

Free and Open Chip Design Tools: Opportunities, Challenges, and Outlook

Designing semiconductor chips has traditionally been costly and controlled by a few major Electronic Design Automation (EDA) vendors—Cadence, Synopsys, and Siemens EDA who dominate with proprietary tools protected by NDAs and restrictive licenses. Fabrication also requires expensive, often export-controlled equipment.… Read More

Why I Think Intel 3.0 Will Succeed

Probably one of the most anticipated semiconductor investor calls was held last week and it did not disappoint. It was Lip-Bu Tan’s first full quarter since he took over as CEO. In the resulting discussions on the SemiWiki Forum I am viewed as overly optimistic of Intel’s recent pivot. That is true, I am optimistic, but my observations… Read More

Cadence at the 2025 Design Automation Conference #62DAC

Cadence, a DAC 2025 industry sponsor, will exhibit in booth 1609 at the 62nd Design Automation Conference at San Francisco’s Moscone West Convention Center.

Highlights:

Paul Cunningham, SVP and GM of the System Verification Group, Cadence, will speak at Cooley’s DAC Troublemaker Panel. This discussion will be an open… Read More