On September 6, 2017, Cadence Design Systems, Lumerical Solutions and PhoeniX Software hosted their second Photonics Summit. As with last year’s summit, this was a two-day event, with the first day including in a myriad of photonics presentations and the second day being a hands-on workshop. The hands-on workshop taught attendees… Read More

Tag: cadence design systems

CDNLive Boston Keynote Address Highlights Emergence of Silicon Photonics

I had the pleasure of being able to attend the CDNLive event held in the Boston, MA area last month and I was pleasantly surprised to see that Cadence highlighted Silicon Photonics as one of its Keynote topics. MIT Professor Duane Boning gave an excellent overview of the current state of silicon photonics and why he believes it is time… Read More

ARM and Cadence IP Simplify IoT System Design and Verification

As the Internet-of-Things (IoT) markets mature, we are seeing the complexity of IoT systems evolve from simple routing functions that connect IoT edge devices to the cloud into more complex system of systems that manage the interaction between multiple sensor-hubs. IoT sensor-hubs and gateways not only take care of basic care… Read More

Cadence’s Tempus – New Hierarchical Approach for Static Timing Analysis

While at the 54[SUP]th[/SUP] Design Automation Conference (DAC) I had the opportunity to talk with Ruben Molina, Product Management Director for Cadence’s Tempus static timing analysis (STA) tool. This was a good review of how the state-of-the-art for STA has evolved over the last couple decades. While the basic problem hasn’t… Read More

Capture the Light with Integrated Photonics

I wrote up a quick article in the weeks before the Design Automation Conference (DAC) letting readers know that Integrated Photonics were indeed coming to DAC again this year. As a follow up, I attended the DAC presentation, ‘Capture the Light. An Integrated Photonics Design Solution from Cadence, Lumerical and PhoeniX Software’,… Read More

TSMC Unveils More Details of Automotive Design Enablement Platform

At this year’s Design Automation Conference (DAC), TSMC unveiled more details about the design enablement platforms that were introduced at their 23[SUP]rd[/SUP] annual TSMC Technology Symposium earlier this year. I attended a presentation on TSMC’s Automotive Enablement Platform held at the Cadence Theater where TSMC’s… Read More

Photonics at DAC – Integrated Electronic/Photonic Design Flow to be Presented at Cadence Theater

I recently wrote an article on SemiWiki talking about the integrated Electronic/Photonic Design Automation (EPDA) flow that is being developed by Cadence Design Systems, Lumerical Solutions and PhoeniX Software and how that flow is now expanding into the system level through SiP (system in package) techniques.

Up till recently,… Read More

Dear Cadence: Calibre Didn’t Run Any Dracula Decks

After reading the Cadence blog post –“Dracula, Vampire, Assura, PVS: A Brief History” – Dr. Andrew Moore has written the below article where he helps readers get a sense as to what “the year of hell” was like, from one of the key individuals who lived it. Andrew also addresses and corrects some of the “urban legends”… Read More

Cadence Expands Integrated Photonics Beachhead

In November of 2016, I made a bold statement that October 20, 2016 would stand as a watershed day in integrated photonics. The reason for this claim was that GLOBALFOUNDRIES proclaimed that integrated photonics was real and here to stay. The same week I wrote an article about Cadence Design Systems securing a photonic beachhead … Read More

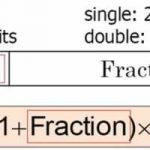

Cadence DSPs float for efficiency in complex apps

Floating-point computation has been a staple of mainframe, minicomputer, supercomputer, workstation, and PC platforms for decades. Almost all modern microprocessor IP supports the IEEE 754 floating-point standard. Embedded design, for reasons of power and area and thereby cost, often eschews floating-point hardware… Read More